# PART NUMBER INDEX

### PART NUMBER

### DESCRIPTION

| PARINUMBER       | DESCRIPTION                                  | PAGE    |

|------------------|----------------------------------------------|---------|

| Product Summary  | All Products                                 | 1 – 3   |

| CLC100           | DC to 500MHz, Linear Amp                     | 7 – 3   |

| CLC102           | DC to 250MHz, Linear High Power Amp          |         |

| CLC103           | Fast Settling, High Current, Wideband Op Amp |         |

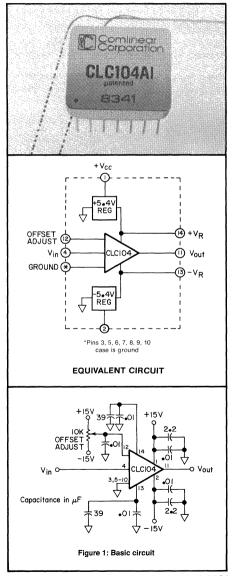

| CLC104           | DC to 1.1GHz, Linear Amp                     |         |

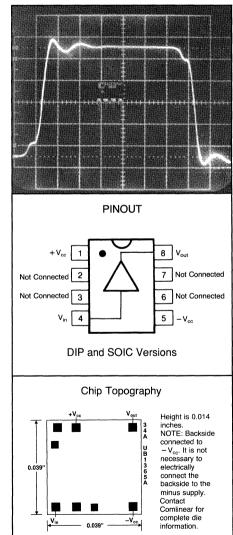

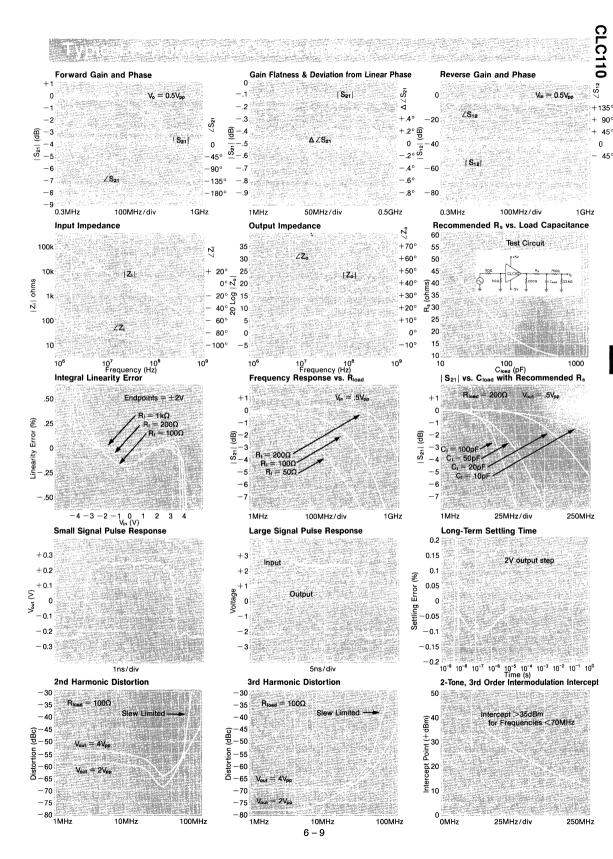

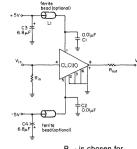

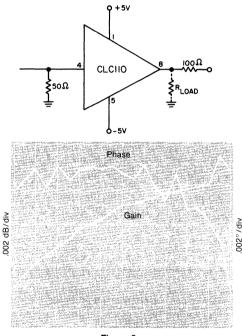

| CLC110           | Wideband, Closed-Loop, Monolithic Buffer Amp |         |

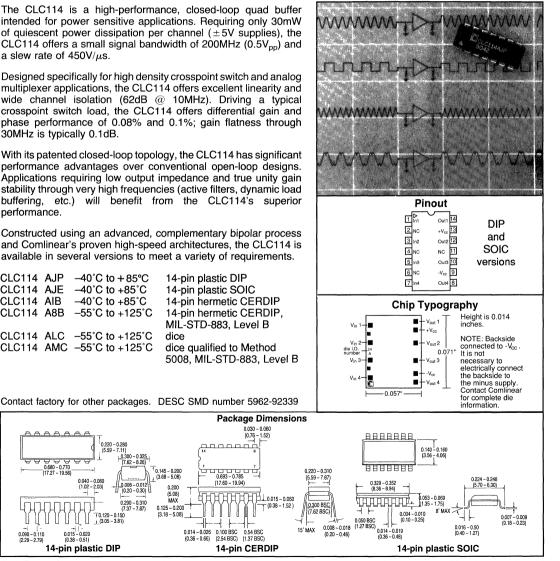

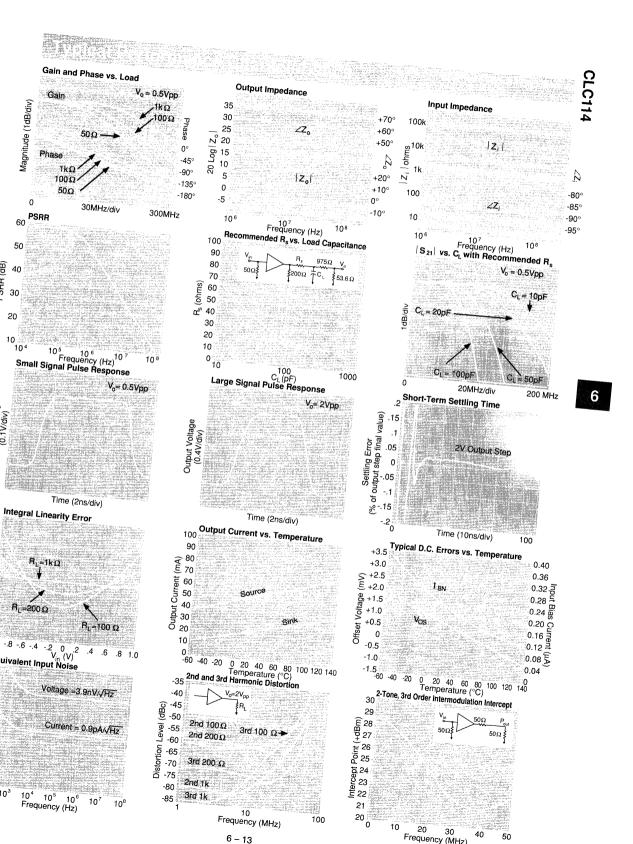

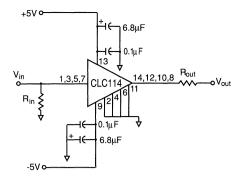

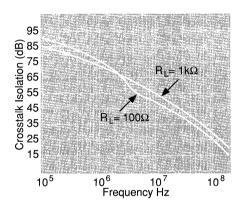

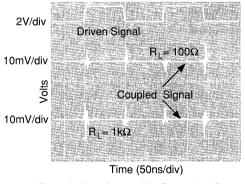

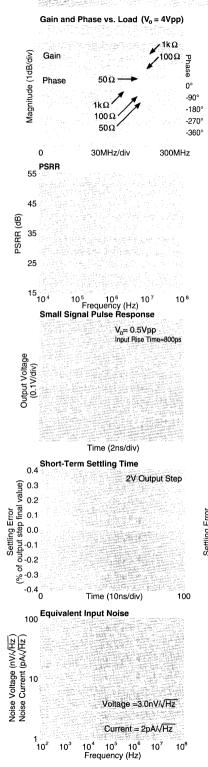

| CLC114           | Quad, Low-Power, Video Buffer                |         |

| CLC115           | Quad, Closed-Loop, Monolithic Buffer         |         |

| CLC140           | Wideband PMT Amp                             |         |

| CLC142           | Wide Dynamic Range, Power Amp                |         |

| CLC142<br>CLC143 | High Fidelity Pulse Amp                      |         |

|                  |                                              |         |

| CLC144           | Very Wideband, Pulse Amp                     |         |

| CLC146           | FET Input Cable Driver                       |         |

| CLC160           | High Power, Driver Amp                       |         |

| CLC162           | Low Distortion, Low Gain Amp                 |         |

| CLC163           | Low Distortion, High Gain Amp                |         |

| CLC166           | Low DC Offset, Wideband Amp                  |         |

| CLC167           | Low DC Offset, High Power, Output Amp        |         |

| CLC200           | Fast Settling, Wideband Op Amp               | .3 – 11 |

| CLC201           | Fast Settling, Wideband Op Amp               |         |

| CLC203           | Fast Settling, High Current, Wideband Op Amp |         |

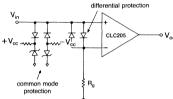

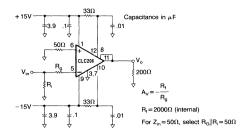

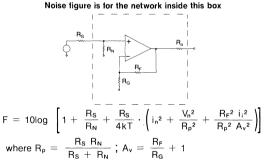

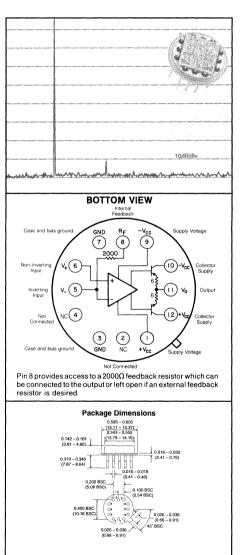

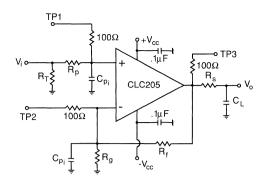

| CLC205           | Overdrive-Protected, Wideband Op Amp         | .3 – 23 |

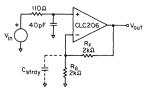

| CLC206           | Overdrive-Protected, Wideband Op Amp         | .3 – 27 |

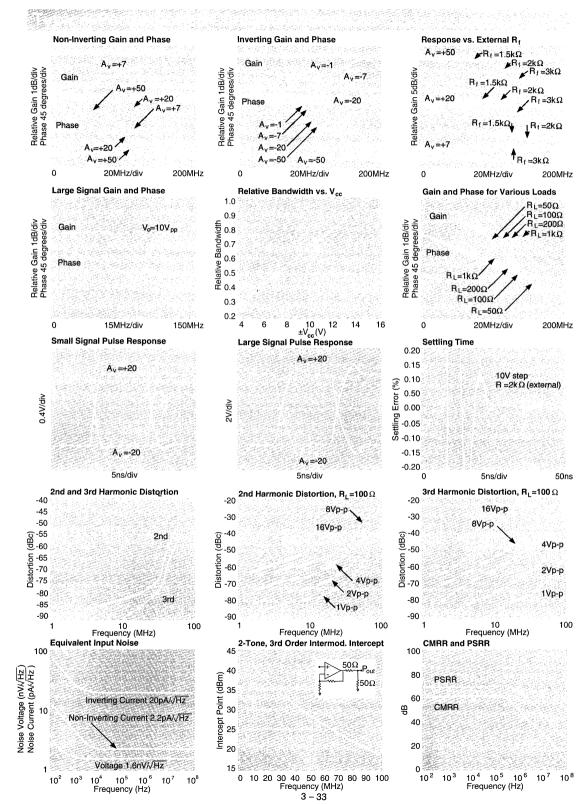

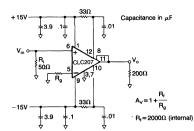

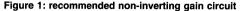

| CLC207           | Low Distortion, Wideband Op Amp              | .3 – 31 |

| CLC220           | Fast Settling, Wideband Op Amp               |         |

| CLC221           | Fast Settling, Wideband Op Amp               | .3 – 39 |

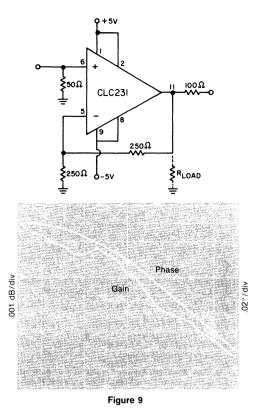

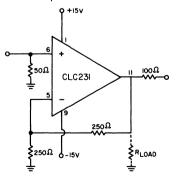

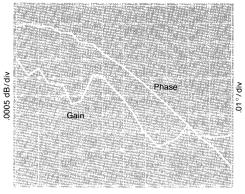

| CLC231           | Fast Settling, Wideband Buff-Amp™            | .3 – 43 |

|                  | $(Av = \pm 1 \text{ to } \pm 5)$             |         |

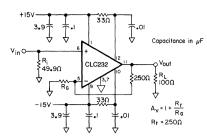

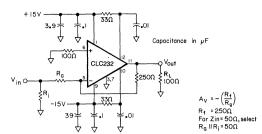

| CLC232           | Low Distortion, Wideband Op Amp              | 3 – 47  |

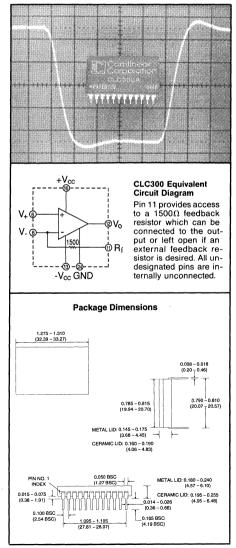

| CLC300           | Wideband, High Speed, Op Amp                 |         |

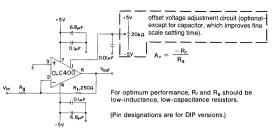

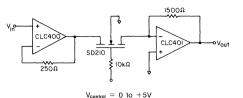

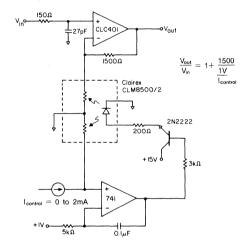

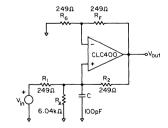

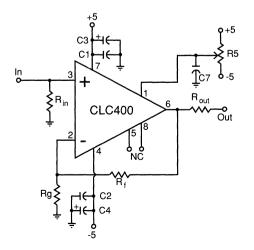

| CLC400           | Fast Settling, Wideband, Low-Gain,           |         |

| 020400           | Monolithic Op Amp                            | .0 00   |

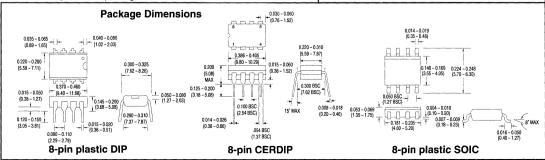

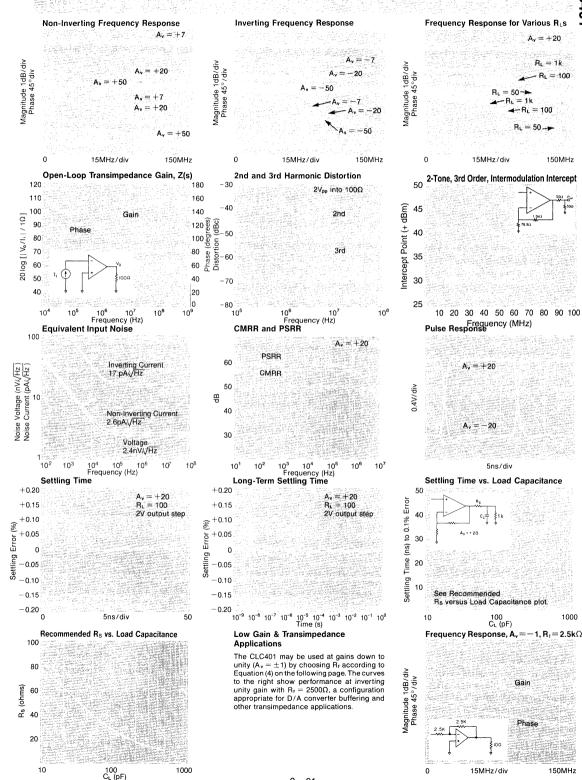

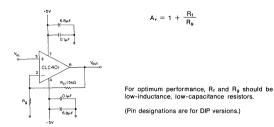

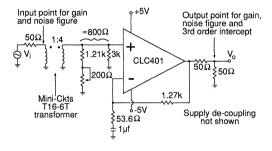

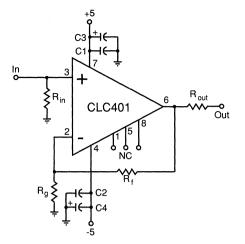

| CLC401           | Fast Settling, Wideband, High-Gain,          | 3 - 59  |

| 020401           | Monolithic Op Amp                            | .0 - 03 |

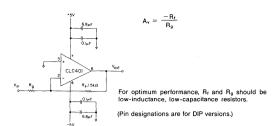

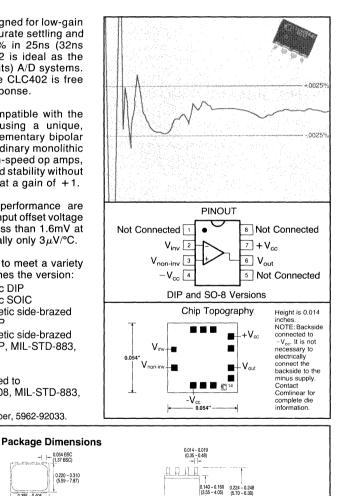

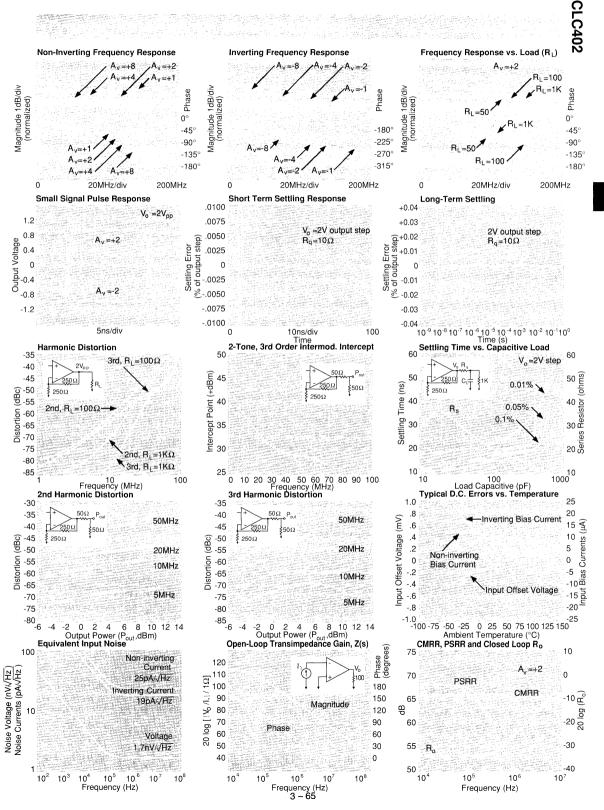

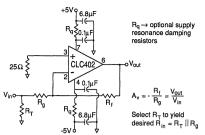

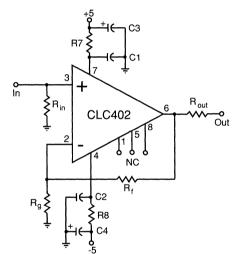

| CLC402           | Low Gain Op Amp with Fast 14-bit Settling    | 2 62    |

|                  |                                              |         |

| CLC404           | Wideband, High Slew Rate,                    | .3 - 67 |

| 01.0400          | Monolithic Op Amp                            | 0 71    |

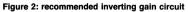

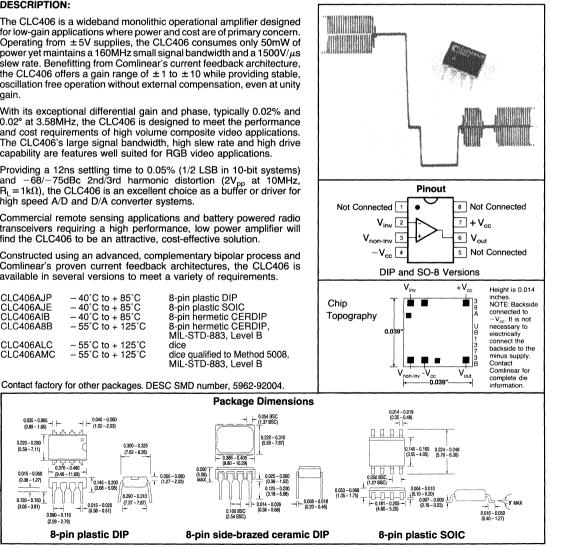

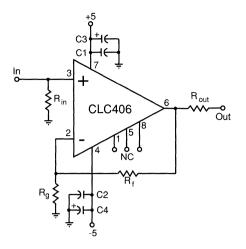

| CLC406           | Wideband, Low Power, Monolithic Op Amp       |         |

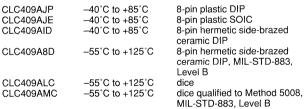

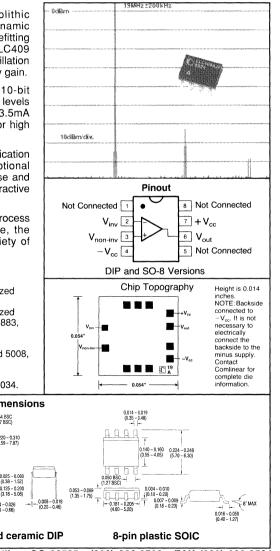

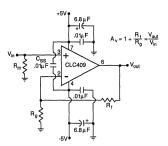

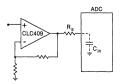

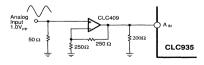

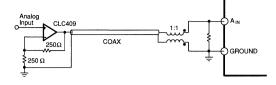

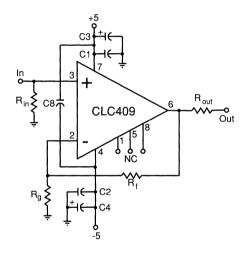

| CLC409           | Very Wideband, Low Distortion,               | .3 - 75 |

|                  | Monolithic Op Amp                            |         |

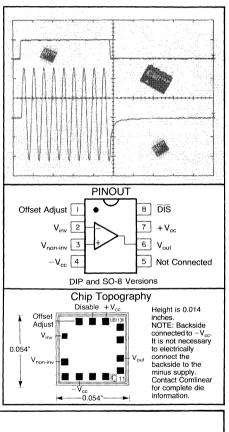

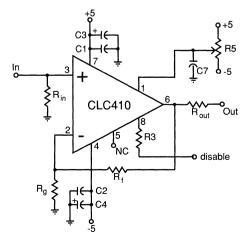

| CLC410           | Fast Settling, Video Op Amp with Disable     |         |

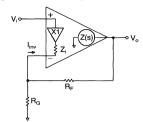

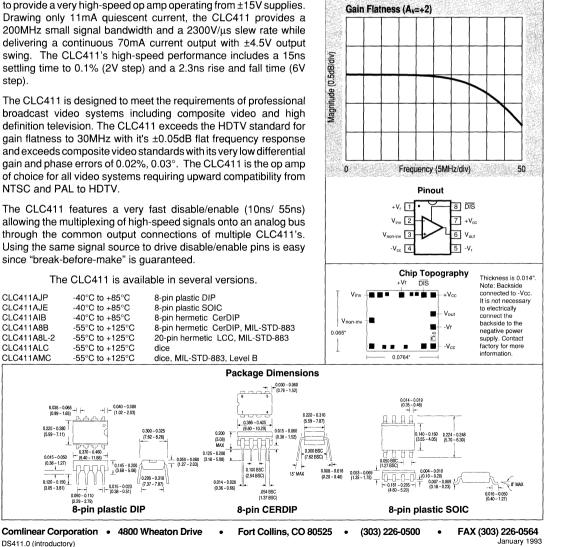

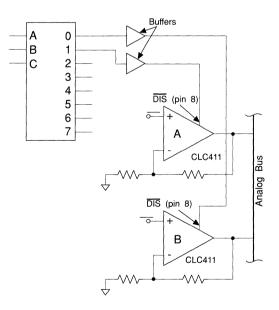

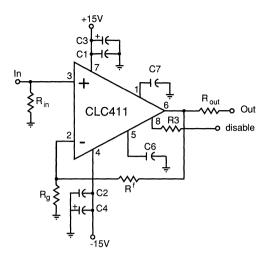

| CLC411           | High Speed Video Op Amp with Disable         |         |

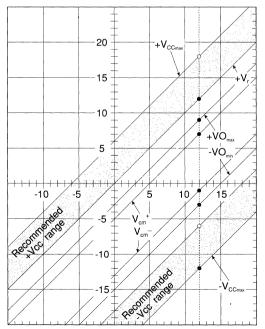

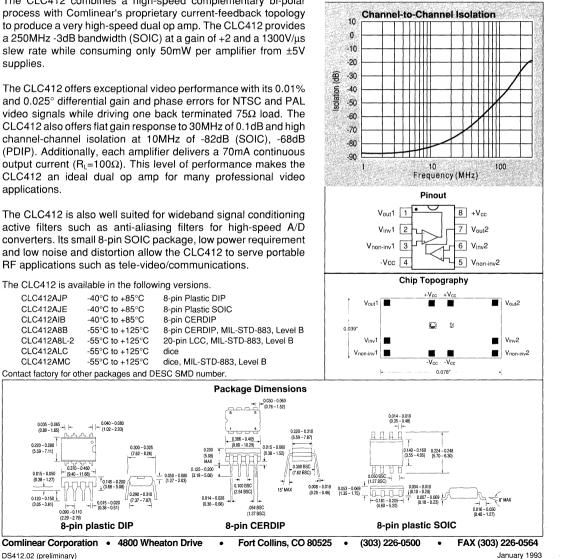

| CLC412           | Dual, Wideband, Low-Power Monolithic         |         |

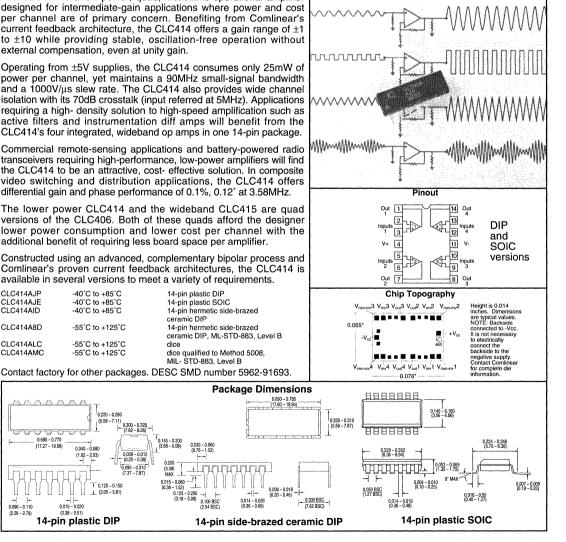

| CLC414           | Quad, Low-Power, Monolithic Op Amp           |         |

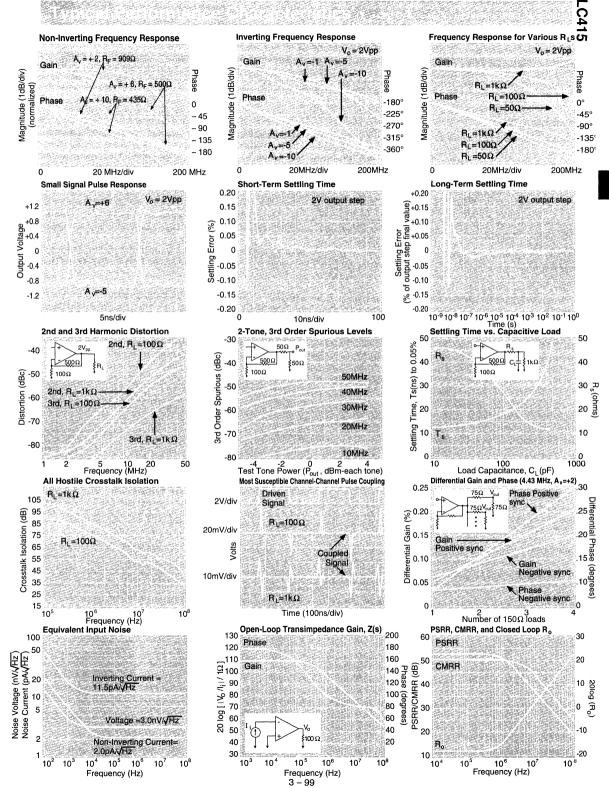

| CLC415           | Quad, Wideband Monolithic Op Amp             |         |

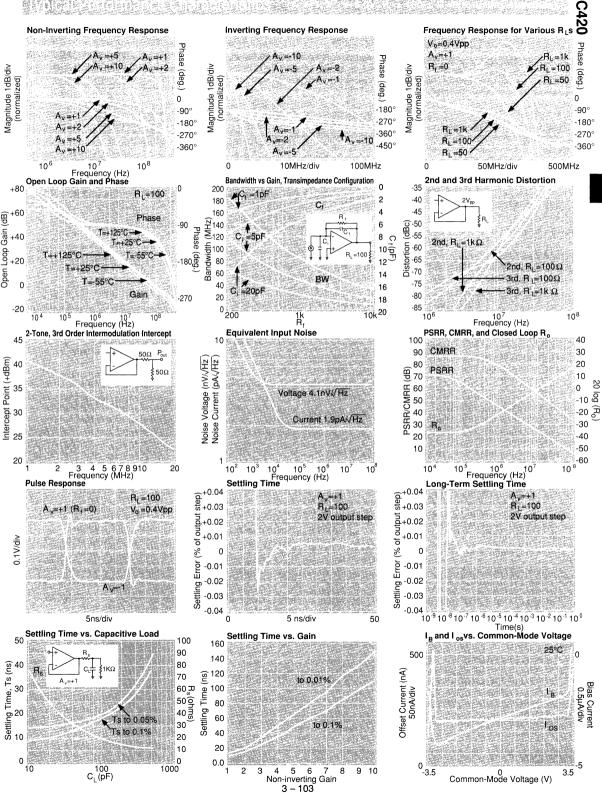

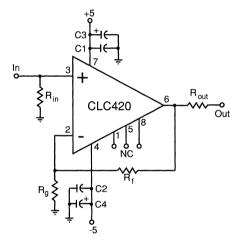

| CLC420           | High-Speed, Voltage Feedback Op Amp          |         |

| CLC422           | High-Gain, Voltage Feedback Op Amp           |         |

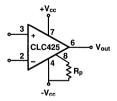

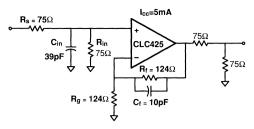

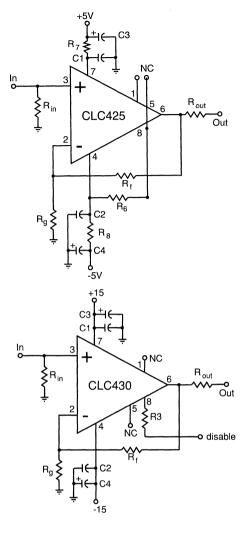

| CLC425           | Ultra Low Noise, Wideband Op Amp             |         |

| CLC430           | Low Gain Op Amp with Disable                 |         |

|                  |                                              |         |

| CLC500   | High-Speed, 12-Bit Settling,Contact factory     |

|----------|-------------------------------------------------|

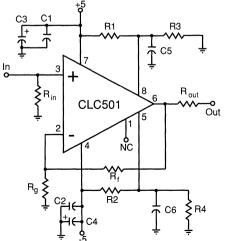

| CLC501   | High Speed, Output Clamping Op Amp              |

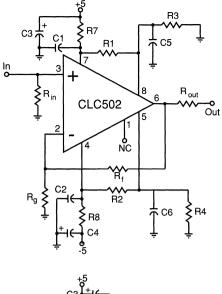

| CLC502   | Clamping, Low Gain Op Amp with                  |

| 010001   | Fast 14-bit Settling                            |

| CLC505   | High Speed, Programmable Supply Current,        |

|          | Monolithic Op Amp                               |

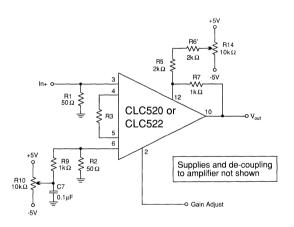

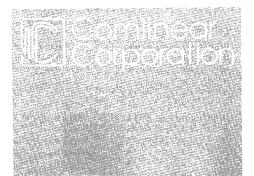

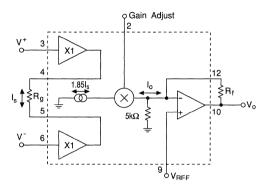

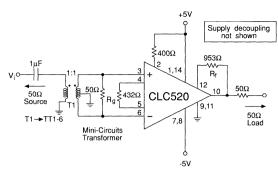

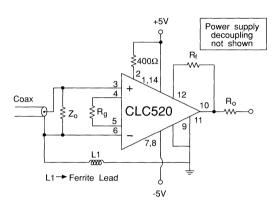

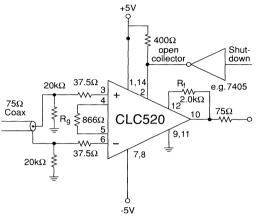

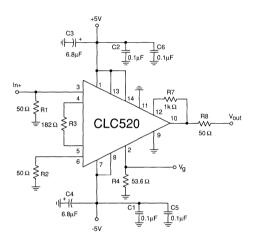

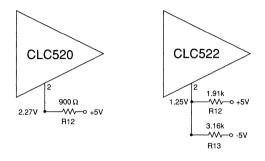

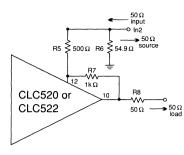

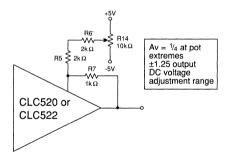

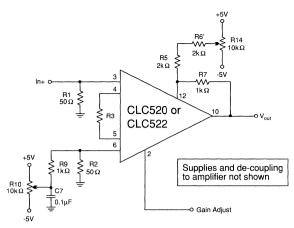

| CLC520   | Amplifier with Voltage Controlled Gain AGC+Amp  |

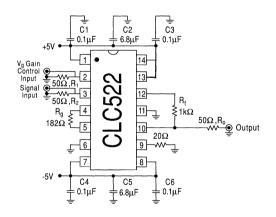

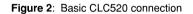

| CLC522   | Wideband, Variable Gain Amp5 – 9                |

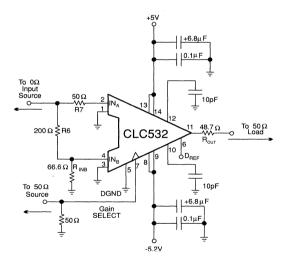

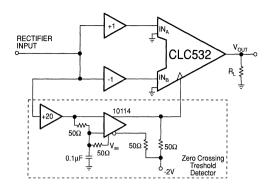

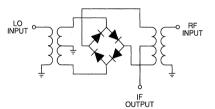

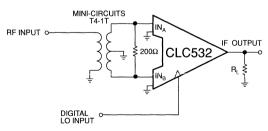

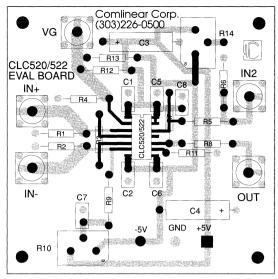

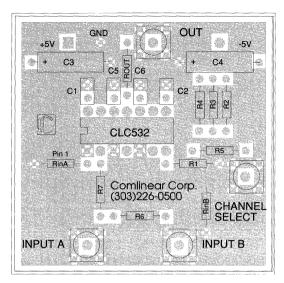

| CLC532   | High Speed, 2:1, Analog Multiplexer8 – 3        |

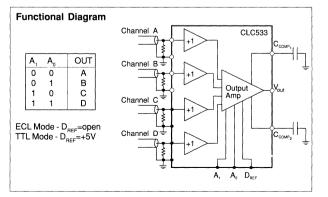

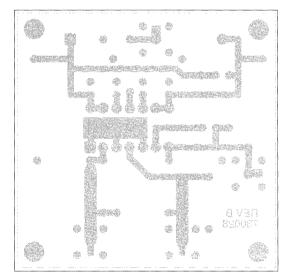

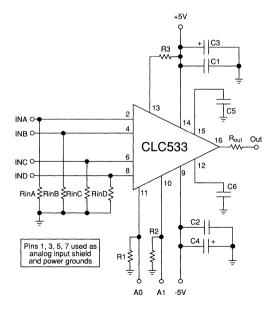

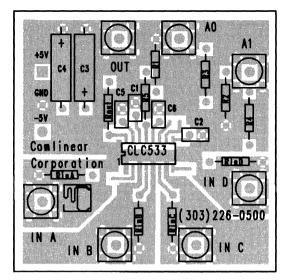

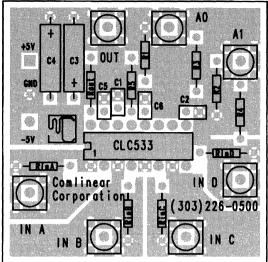

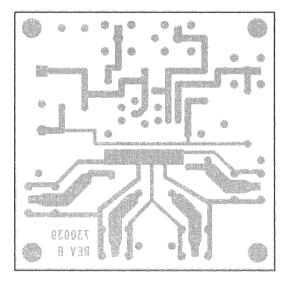

| CLC533   | High Speed, 4:1, Analog Multiplexer8 – 11       |

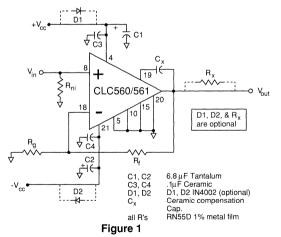

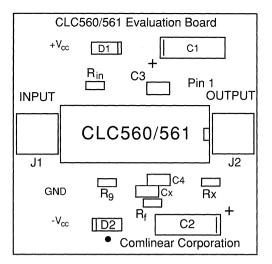

| CLC560   | Wideband, Low Distortion, DriveR-amp4 - 3       |

| CLC561   | Wideband, Low Distortion, DriveR-amp 4 – 15     |

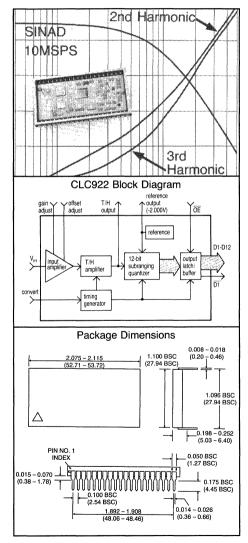

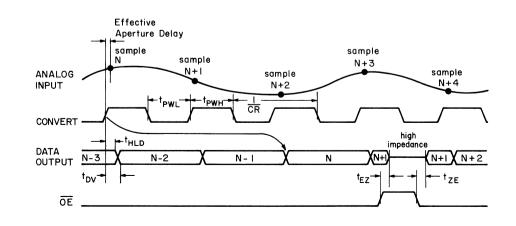

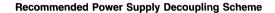

| CLC922   | Dual Supply, 12-bit 10MSPS, A/D Converter10 – 3 |

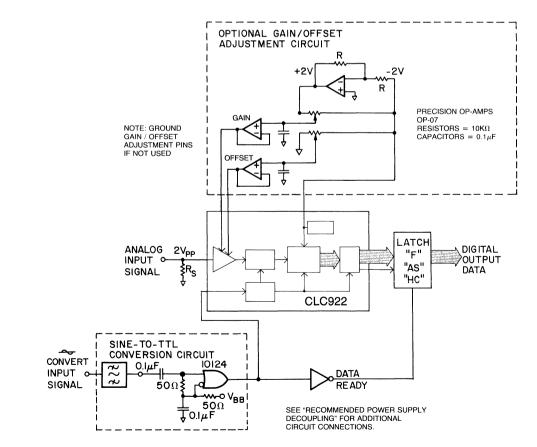

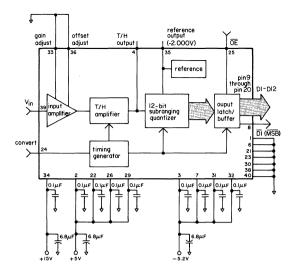

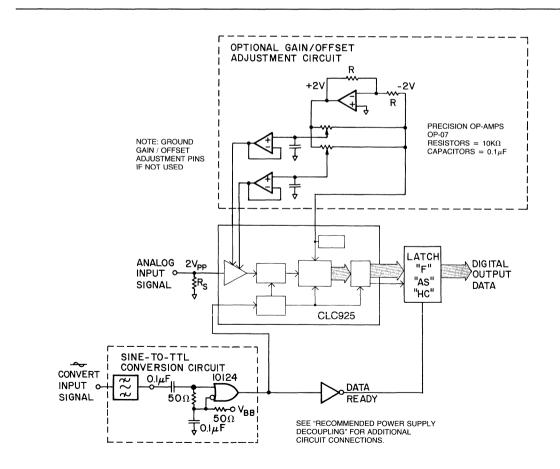

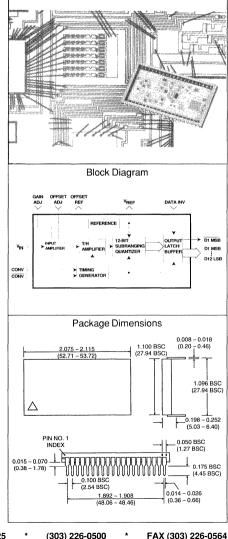

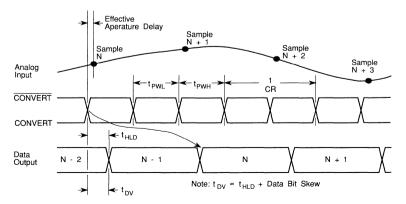

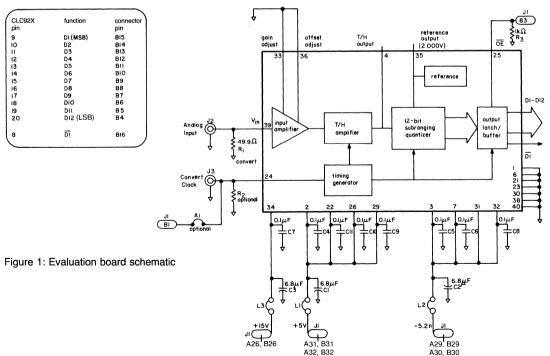

| CLC925   | 12-Bit, 10MSPS, A/D Converter10 – 15            |

| CLC926   | 12-Bit, 10MSPS, A/D Convertercontact factory    |

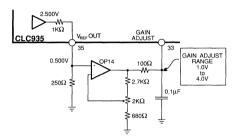

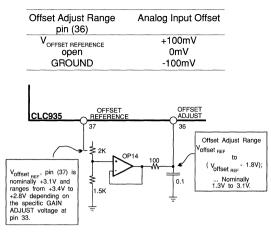

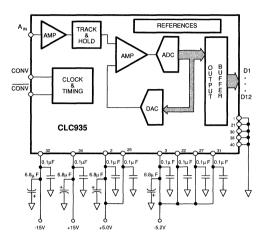

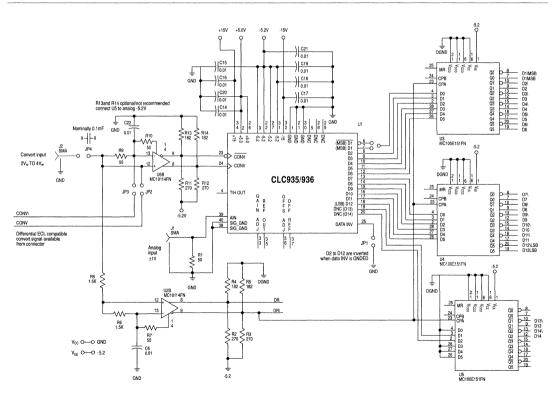

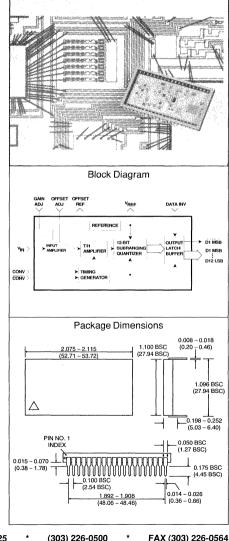

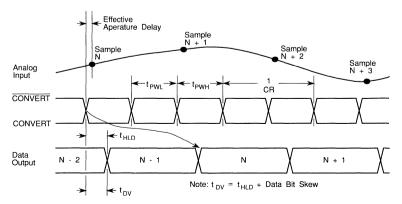

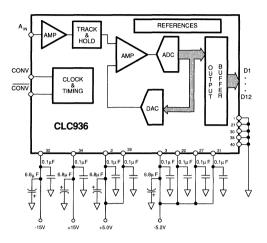

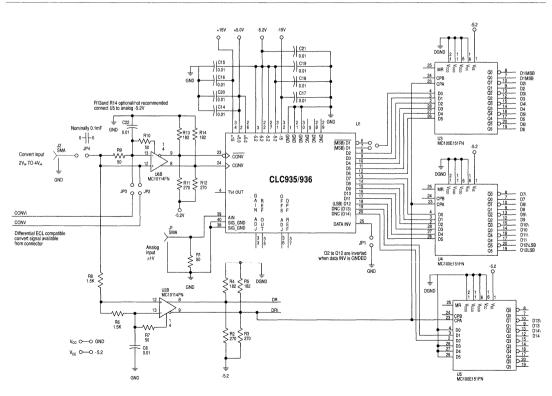

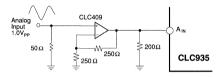

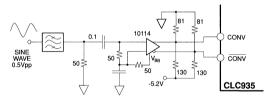

| CLC935   | 12-Bit, 15MSPS, A/D Converter10 – 27            |

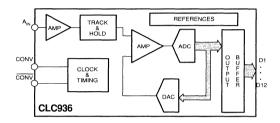

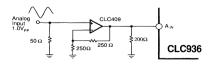

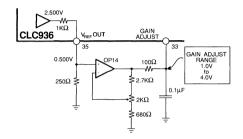

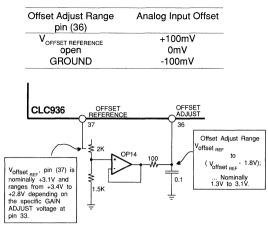

| CLC936   | 12-Bit, 20MSPS, A/D Converter10 – 39            |

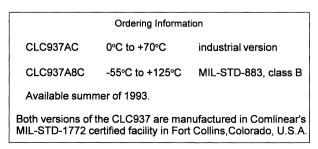

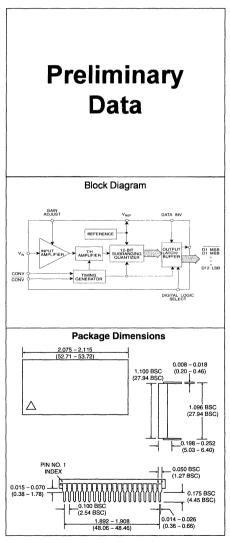

| CLC937   | 12-Bit, 25.6MSPS, A/D Converter10 – 51          |

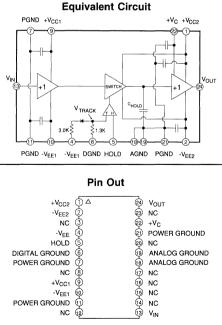

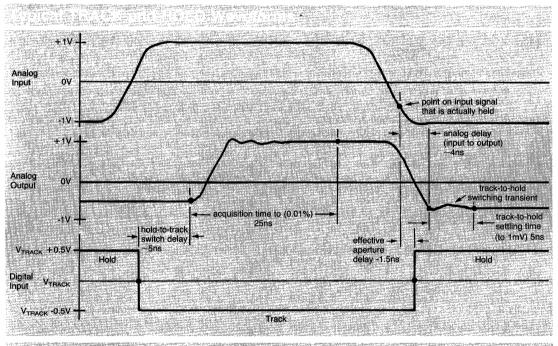

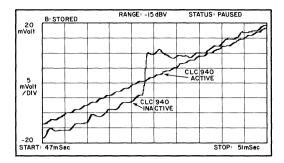

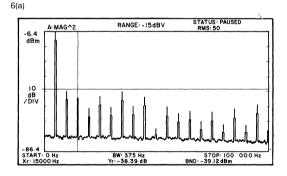

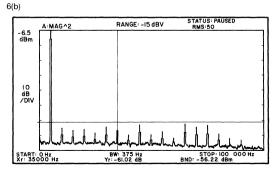

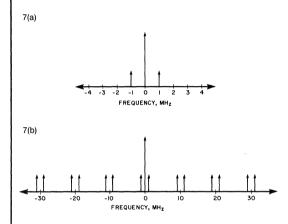

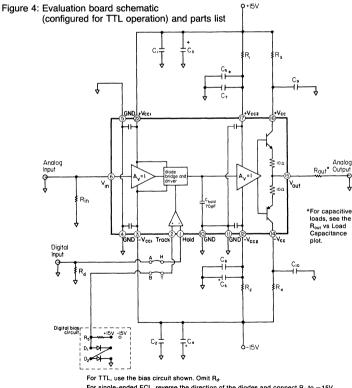

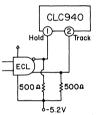

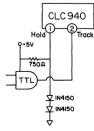

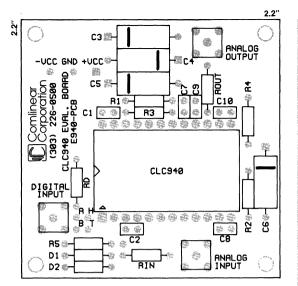

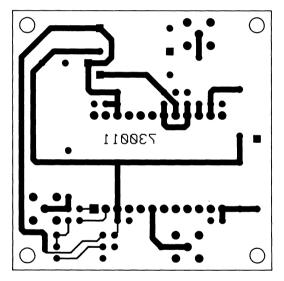

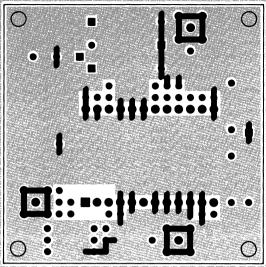

| CLC940   | Fast-Sampling, Wideband,9 – 3                   |

|          | Track & Hold Amp                                |

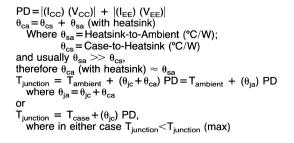

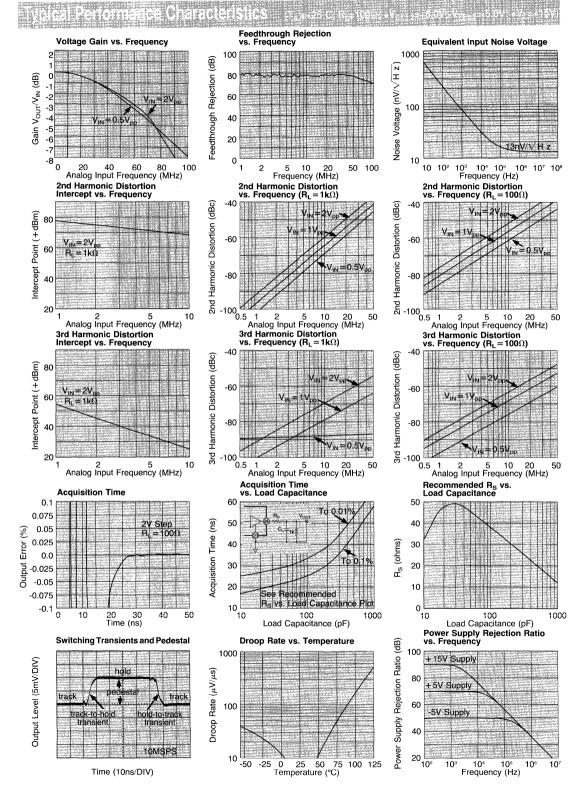

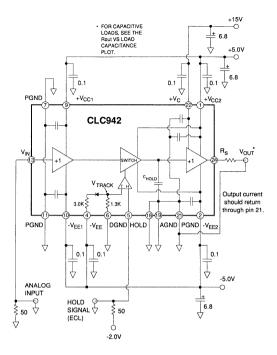

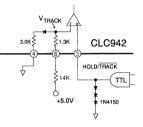

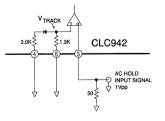

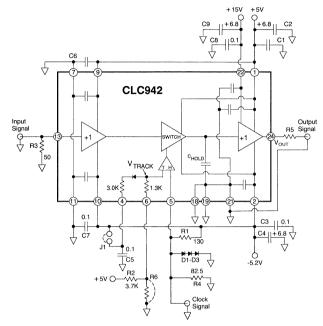

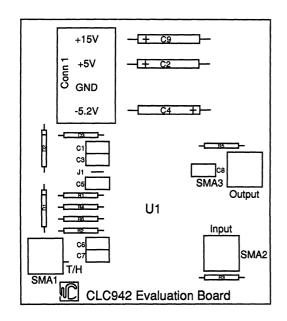

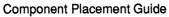

| CLC942   | 12-Bit, Fast Sampling, Wideband,9 – 9           |

|          | Track & Hold Amp                                |

| CLC950   | 12-Bit, 25.6MSPS, A/D Converter10 – 55          |

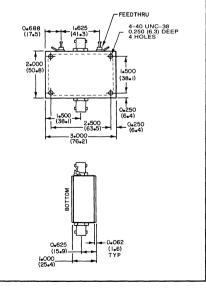

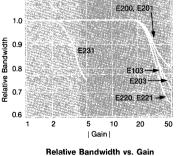

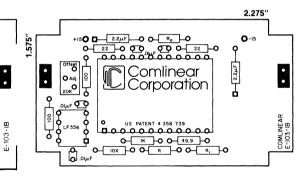

| E Series | Encased Amps7 – 9                               |

|          |                                                 |

L

| 1  | Product Summary                                |

|----|------------------------------------------------|

| 2  | Quality and Reliability                        |

| 3  | Operational Amplifiers                         |

| 4  | High Power Amplifiers                          |

| 5  | Variable Gain Amplifiers                       |

| 6  | Unity Gain Buffer and Linear Amplifiers        |

| 7  | Modular and Encased Amplifiers                 |

| 8  | Analog Multiplexers                            |

| 9  | Track & Hold Amplifiers                        |

| 10 | Analog-to-Digital Converters                   |

| 11 | Application Notes                              |

| 12 | Spice Models                                   |

| 13 | Packaging and Die Information                  |

| 14 | Product Accessories and Evaluation Boards      |

| 15 | Ordering Guide/Return and Warranty Information |

| 16 | Sales Offices/Distributors                     |

200

33

astrofj NERO

# **1993-94 Databook** Solutions with Speed

Comlinear Corporation, located in Fort Collins, Colorado, is a manufacturer and supplier of high-performance analog signal processing components. Comlinear's signal conditioning product line includes high-speed hybrid and monolithic operational amplifiers, buffers, and clamping amplifiers. The data converter product line includes track/hold amplifiers and analog-to-digital converters. The corporate philosophy is to focus development on products that make a significant contribution toward solving customer problems. The result has been the ever-expanding line of high-performance products included in the following pages.

The company is housed in a custom-built facility, which is DESC certified to MIL-STD-1772. Manufacturing, Quality Assurance, Research and Development, Administration and Marketing are centered in this location.

Comlinear's proprietary signal processing components are sold worldwide to a diverse group of commercial, industrial and military customers. Representative application areas include communications (satellite systems, radar, fiber optics), avionics (electronic counter measures, instrumentation), video (high resolution displays, video processing and distribution), and automatic test equipment.

Comlinear believes that a deeply-rooted dedication to quality is a critical path to customer satisfaction. Statistical process control and team quality concepts are approaches used throughout the company to improve quality in activities ranging from new product releases to order processing to shipping. It is only through this comprehensive approach to quality that lasting improvements in all product and service areas can be achieved.

Comlinear's goal is to offer our customers superior products with quality and service second to none.

### **DISCLAIMER INFORMATION**

### Warning-Life Support Systems

Comlinear's products are not authorized for use in life support devices or systems without express written authorization from the President of Comlinear Corporation. Life support devices or systems are those which are intended to support or sustain life, and whose failure to perform when properly used in accordance with the instructions provided can be reasonably expected to result in significant personal injury or death to the user.

### LIMITATION ON WARRANTY AND REMEDIES

Comlinear makes no warranty with respect to its products except as expressly set forth in its standard conditions of sale. All implied warranties, including any implied warranty of merchantability or fitness for a particular purpose, are hereby disclaimed. Any warranty extended on Comlinear products is limited to the replacement of the defective component and does not cover personal injury, property damage, or incidental, consequential or special damages.

### DISCLAIMER

Information on all products and services furnished herein by Comlinear Corporation is believed to be accurate and reliable at the time of this printing. Comlinear reserves the right to make changes to its products and specifications at any time without notice. Comlinear Corporation does not assume responsibility for the use of the products described herein.

The products in this databook are covered under one or more of the following patents: 4,358,739; 4,502,020; 4,628,279; 4,639,685; 4,713,628; 4,757,275; 4,766,367; 4,780,689; 5,049,653 (other patents pending).

# Product Summary Contents

# Product TypePageModular Series1 – 3Unity Gain and Linear Amplifiers1 – 3Operational Amplifiers1 – 4High Power Amplifiers1 – 5Variable Gain Amplifiers1 – 5Analog Multiplexers1 – 5Analog-to-Digital Converters1 – 6Track and Hold Amplifiers1 – 6Packaging Selection Guide1 – 7

1 – 2

# **Product Summary Guide**

### Modular Series

| Nodel <sup>1, 3</sup> |                    | andwidth<br>(Hz) | Gain <sup>2</sup><br>(dB)            | Gain Flatness<br>(db to MHz) | R <sup>in</sup> & R <sup>out</sup><br>(Ω) | Output at -1dB Gair<br>Compression (+dBm@l |    | Rise & Fall<br>Time (nsec) | Overload Recovery<br>Time (nsec)                                |    | Group<br>ay (nsec) | Deviation from<br>Linear Phase (°) | Equivalent Input<br>Noise (µV <sub>rms</sub> ) | Package                          |

|-----------------------|--------------------|------------------|--------------------------------------|------------------------------|-------------------------------------------|--------------------------------------------|----|----------------------------|-----------------------------------------------------------------|----|--------------------|------------------------------------|------------------------------------------------|----------------------------------|

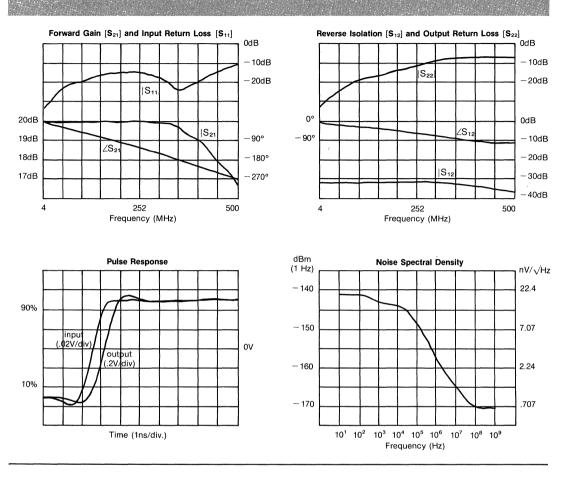

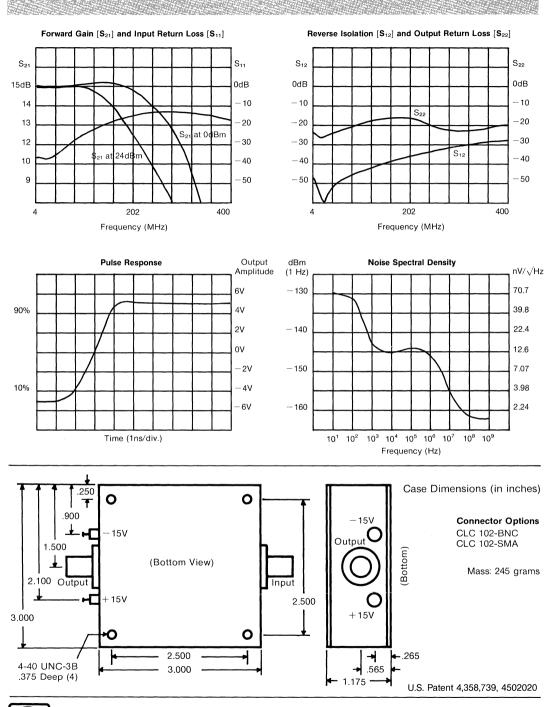

| CLC100                | 5                  | 500              | 20                                   | ± 0.05 to 300                | 50                                        | 12 @ 500                                   |    | 0.600                      | <2                                                              |    | 1.4                | 1                                  | 20                                             | 1.9" X 4.14"<br>Mach. Alum. Case |

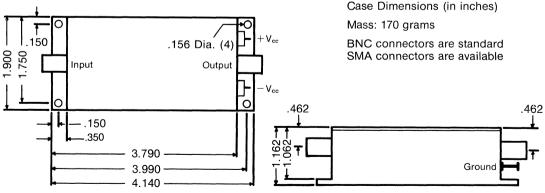

| CLC102                | 2                  | 250              | 15                                   | ± 0.4 to 200                 | 50                                        | 26 @ 100                                   |    | 1.6                        | _                                                               |    | 2.3                | 1                                  | 46                                             | 3.0" X 3.0"<br>Mach. Alum. Case  |

| Mode                  | el <sup>1, 3</sup> | (match           | ain<br>ed Ioad<br>IB)                |                              | dwidth<br>Sout<br>t, dBm)                 | input<br>impedance<br>(Ω)                  | ir | output<br>mpedance<br>(Ω)  | V <sub>out</sub> , I <sub>out</sub><br>(matched load<br>(V, mA) | )  |                    | oower<br>ply range<br>(V)          | output<br>current<br>(mA)                      | input<br>voltage<br>(V)          |

| CLC                   | 140                | 2                | 20                                   | 50                           | 0, 10                                     | 50                                         |    | 50                         | ± 1.25, ± 15                                                    |    | ± 5                | 5 to ± 16                          | ± 20                                           | ± 0.5                            |

| CLC                   | 142                | 15               | (inv.)                               | 25                           | 0, 18                                     | 50                                         |    | 50                         | ± 10, ± 250                                                     |    | ± 1                | 2 to ± 16                          | ± 250                                          | ±2                               |

| CLC                   | 143                | 15               | (inv.)                               | 22                           | 0, 18                                     | 50                                         |    | 50                         | ± 10, ± 250                                                     |    | ± 1                | 2 to ± 16                          | ± 250                                          | ± 2                              |

| CLC                   | 144                | 1                | 14                                   | 110                          | 00, 12                                    | 50                                         |    | 50                         | ± 1.5, ± 35                                                     |    | ± 9                | ) to ± 16                          | ± 40                                           | ± 0.5                            |

| CLC                   | 146                |                  | 0                                    | 22                           | 0, 10                                     | FET                                        |    | 50 or 75                   | ± 5, ± 100                                                      |    | ± 1                | 0 to ± 16                          | ± 150                                          | $\pm V_{cc}$                     |

| Mode                  | el <sup>1, 3</sup> | (oper            | ain<br>1 Ioad)<br>"/V <sub>i</sub> ) |                              | dwidth<br>o <sub>out</sub><br>, dBm)      | input<br>impedance<br>(Ω)                  | ir | output<br>mpedance<br>(Ω)  | V <sub>out</sub> , (open load<br>I <sub>out</sub><br>(V, mA)    | 1) |                    | power<br>ply range<br>(V)          | output<br>current<br>(mA)                      | input<br>voltage<br>(V)          |

| CLC                   | 160                | 5 t              | o 20                                 | 17                           | 0, 18                                     | 50 to 1k                                   |    | 50 to 200                  | ± 10, ± 200                                                     |    | ± 11               | 0, to ± 16                         | ± 250                                          | $\pm V_{cc}$                     |

| CLC                   | 162                | 21               | to 5                                 | 25                           | 0, 10                                     | 50 to 1k                                   |    | 50 to 1k                   | ± 10, ± 100                                                     |    | ±5                 | 5 to ± 16                          | ± 150                                          | ±6                               |

| CLC                   | 163                | 5 te             | o 40                                 | 17                           | 0, 10                                     | 50 to 1k                                   |    | 50 to 1k                   | ± 10, ± 100                                                     |    | ±5                 | 5 to ± 16                          | ± 150                                          | note 1                           |

| CLC                   | 166                | 10               | to 40                                | 17                           | 0, 10                                     | 50 to 200                                  |    | 50 to 1k                   | ± 10, ± 50                                                      |    | ±5                 | i to ± 16                          | ± 75                                           | note 1                           |

| CLC                   | 167                | 10 1             | to 40                                | 15                           | 0, 10                                     | 50 to 200                                  |    | 50 to 1k                   | ± 10, ± 200                                                     |    | +1                 | 0 to ± 16                          | ± 200                                          | note 1                           |

NOTE: THE OUTPUT MUST NOT BE OVERDRIVEN FOR THESE PARTS. THEREFORE THE MAXIMUM  $\pm V_{in}$  WILL BE  $\pm (|V_{oc}| - 4V)/A_{v}$ .

### Unity-Gain and Linear Amplifiers (typical specifications, + 25°C, $R_s = 50\Omega$ )

| Model <sup>1,3</sup> | Key Features                         | - 3db Bandwidth | Gain | Full Power BW                | Harmonic Distortion              | Settling Time | Output  | Slew Rate | Output Offset   | Test                                                                | T |   | V            | ersic | ons' |   |

|----------------------|--------------------------------------|-----------------|------|------------------------------|----------------------------------|---------------|---------|-----------|-----------------|---------------------------------------------------------------------|---|---|--------------|-------|------|---|

| mouor                | noy i outuroo                        | (MHz)           |      | (MHz @ V <sub>pp</sub> , RL) | (dBc @ 20MHz, 2V <sub>pp</sub> ) |               | (V, mA) | (V/µsec)  | Drift(mV,µV/°C) | Conditions                                                          | J | Е | Π            | ĸ     | M 8  | L |

| CLC104               | Very Wideband<br>Linear Amp          | 1100            | 14dB | 1050 @ 2, 50                 | - 44, - 43                       | 1.2, 0.8      | 1.5, 40 | 6000      | 50, 375         | $\begin{array}{c} R_{L} \ 50\Omega \\ V_{cc} = \pm 15V \end{array}$ | Ι |   | $\checkmark$ |       |      | Τ |

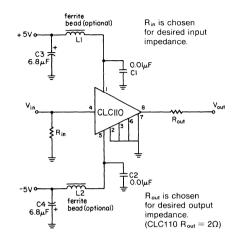

| CLC110               | Closed-Loop Design<br>Low Distortion | 730             | 0.97 | 90 @ 5, 100                  | - 65, - 65                       | 5, 0.2        | 4, 70   | 800       | 2, 20           | $\begin{array}{l} R_{L} = 100\Omega \\ V_{cc} = \pm 5V \end{array}$ | V | V | V            |       | 1    | V |

| CLC114               | Quad Buffer<br>Low Power             | 200             | 0.97 | 95, @ 2, 100                 | - 50, - 58                       | 10, 0.1       | 4, 25   | 450       | .5, 9           | $\begin{array}{l} R_{L} = 100\Omega \\ V_{cc} = \pm 5V \end{array}$ | V | V | 1            |       | V    | V |

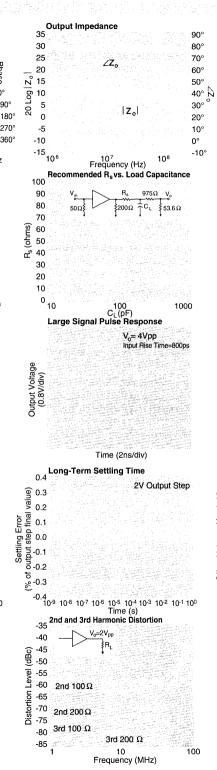

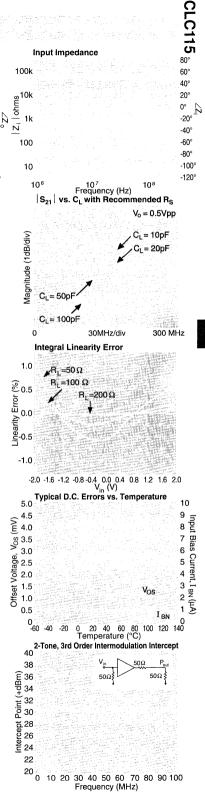

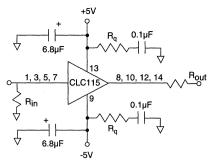

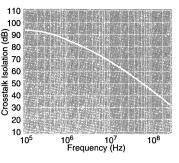

| CLC115               | Quad Buffer<br>High Speed            | 700             | 0.99 | 270 @ 4, 100                 | - 62, - 62                       | 12, 0.1       | 60      | 2700      | 2, 25           | $\begin{array}{l} R_{L} = 100\Omega \\ V_{cc} = \pm 5V \end{array}$ | V | V | $\checkmark$ |       | V    |   |

| Ma                             | K. F.                                       | - 3d                            | B Bandwid                   | th (MHz)                    | Colo Dourou                                                      | Full Decision Diff                                         | Comilia - Ti               | 0                | Olaus Data            | In much Office at                 | Test                                                                     |            | Ve         | ersio | ns' |   |

|--------------------------------|---------------------------------------------|---------------------------------|-----------------------------|-----------------------------|------------------------------------------------------------------|------------------------------------------------------------|----------------------------|------------------|-----------------------|-----------------------------------|--------------------------------------------------------------------------|------------|------------|-------|-----|---|

| Model 1,3                      | Key Features                                | $ \mathbf{A}_{\mathbf{v}}  = 4$ | A <sub>v</sub>   = 20       | $ A_v  = 40$                | Gain Range<br>(A <sub>v</sub> = V <sub>o</sub> /V <sub>i</sub> ) | Full Power BW<br>(MHz @ V <sub>pp</sub> , R <sub>L</sub> ) | Settling Time<br>(nsec, %) | Output<br>(V,mA) | Slew Rate<br>(V/µsec) | Input Offset<br>Drift (mV, μV/°C) | Test<br>Conditions                                                       | J          | EI         | к     | м   | 8 |

| CLC103A                        | High Output Current                         | 170                             | 150                         | 130                         | ± 1 to 40                                                        | 80 @ 20, 100                                               | 10, 0.4                    | ± 11, 200        | 6000                  | 10, 50                            | $R_L = 100\Omega$<br>$V_{cc} = \pm 15V$                                  |            | V          |       | A   |   |

| CLC203A                        | High Output Current                         | 180                             | 160                         | 130                         | ± 1 to 50                                                        | 60 @ 20, 100                                               | 15, 0.2                    | ± 11, 200        | 6000                  | 0.5, 5                            | $\begin{array}{c} R_{L} = 100\Omega \\ V_{cc} = \pm 15V \end{array}$     | Π          | 1          | Π     | V   |   |

| CLC200A                        | General Purpose                             | 100                             | 95                          | 90                          | ± 1 to 50                                                        | 25 @ 20, 200                                               | 18, 0.1<br>25, 0.02        | ± 12, 100        | 4000                  | 10, 35                            | $R_L = 200\Omega$<br>$V_{cc} = \pm 15V$                                  | Π          | V          | Π     | Π   | ľ |

| CLC201A                        | Low Offset and Drift                        | 100                             | 95                          | 90                          | ± 1 to 50                                                        | 50 @ 20, 200                                               | 18, 0.1<br>30, 0.02        | ± 12, 100        | 4000                  | 0.5, 5                            | $R_L = 200\Omega$<br>$V_{cc} = \pm 15V$                                  | Π          | V          | Π     | Π   |   |

| CLC220A                        | General Purpose                             | 200                             | 190                         | 160                         | ± 1 to 50                                                        | 100 @ 10, 200                                              | 8, .01<br>15, 0.02         | ± 12, 50         | 7000                  | 10, 35                            | $R_L = 200\Omega$<br>$V_{cc} = \pm 15V$                                  | Π          | V          | Π     | Π   | I |

| LC221A                         | Low Offset and Drift                        | 200                             | 170                         | 120                         | ± 1 to 50                                                        | 130 @ 10, 200                                              | 15, 0.1<br>18, 0.02        | ± 12, 50         | 6500                  | 0.5, 5                            | $\begin{array}{c} R_{L} = 200\Omega \\ V_{cc} = \pm 15V \end{array}$     | Π          | 1          | Π     | Π   | I |

| LC205A                         | Overdrive Protected<br>Low Power            | 190                             | 170                         | 120                         | + 7 to + 50<br>- 1 to - 50                                       | 100 @ 10, 200                                              | 22, 0.1<br>24, 0.05        | ± 12, 50         | 2400                  | 3.5, 11                           | $\begin{array}{l} R_{L} = 200\Omega \\ V_{cc} = \pm 15V \end{array}$     | Π          | V          | ٧     |     |   |

| LC206A                         | Overdrive Protected<br>100mA Output Current | 200                             | 180                         | 90                          | + 7 to + 50<br>- 1 to - 50                                       | 70 @ 20, 200                                               | 19, 0.1<br>22, 0.05        | ± 12, 100        | 3400                  | 3.5, 11                           | $\begin{array}{l} R_{L} = 200\Omega \\ V_{cc} = \pm 15V \end{array}$     | Π          | V          | V     |     |   |

| CLC207                         | Low Distortion                              | 250                             | 170                         | 90                          | + 7 to + 50<br>- 1 to - 50                                       | 100 @ 10, 200                                              | 24, 0.05                   | ± 12, 150        | 2400                  | 3.5, 11                           | $\begin{array}{c} R_{L} = 200\Omega \\ V_{\infty} = \pm 15V \end{array}$ | Π          | V          | V     | Π   |   |

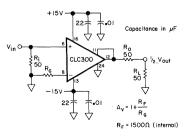

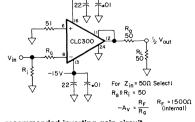

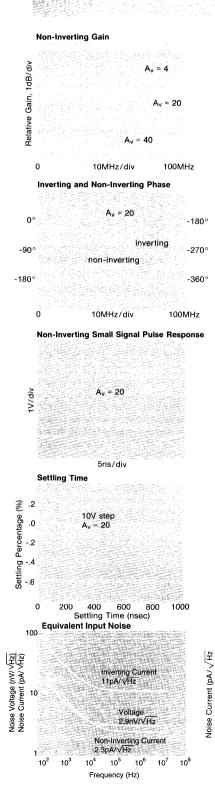

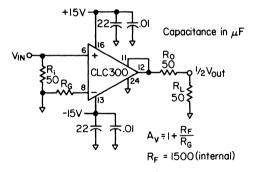

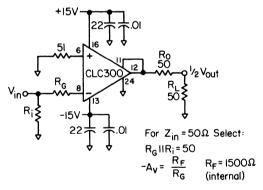

| LC300A                         | Low Cost<br>100mA Output Current            | 105                             | 85                          | 70                          | + 1 to 40                                                        | 45 @ 20, 100                                               | 20, 0.8                    | ± 10, 100        | 3000                  | 10, 25                            | $\begin{array}{l} R_{L} = 100\Omega \\ V_{\infty} = \pm 15V \end{array}$ | Π          | V          | Π     |     |   |

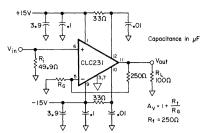

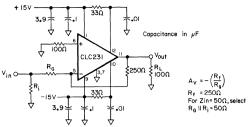

| LC231A<br>uff-Amp <sup>™</sup> | Low Gain<br>Low Power                       | A <sub>v</sub>  =1<br>165       | A <sub>v</sub>  =2<br>165   | A <sub>v</sub>  =5<br>120   | ± 1 to 5                                                         | 95 @ 10, 100                                               | 12, 0.1<br>15, 0.05        | ± 11, 100        | 3000                  | 1, 10                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 15V$                                  | Π          | V          | V     |     |   |

| CLC232                         | Low Distortion                              | A,  = 1<br>220                  | A <sub>v</sub>  =2<br>175   | A <sub>v</sub>  =5<br>110   | ± 1 to 5                                                         | 95 @ 10, 100                                               | 15, 0.05                   | ± 12, 100        | 3000                  | 1, 10                             | $R_L = 100\Omega$<br>$V_m = \pm 15V$                                     | Π          | V          | V     | Π   |   |

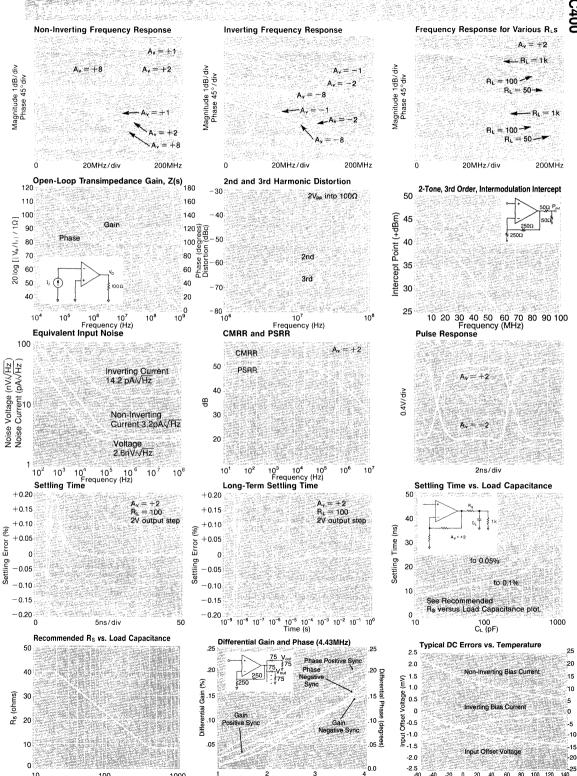

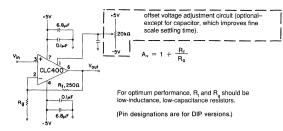

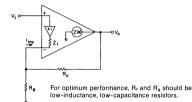

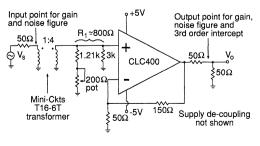

| CLC400                         | Low Cost<br>Low Power                       | A,  = 1<br>220                  | A <sub>v</sub>  =2<br>200   | A <sub>v</sub>  =8<br>60    | ± 1 to 8                                                         | 50 @ 5 100                                                 | 12, 0.05                   | ± 3.5, 70        | 700 (NI)<br>1600 (IN) | 2, 20                             | $R_L = 100\Omega$<br>$V_m = \pm 5V$                                      | 1          | <b>√</b> √ | Π     |     |   |

| CLC401                         | Low Cost<br>Low Power                       | A <sub>,</sub>  =7<br>180       | A <sub>v</sub>  =20<br>150  | A <sub>v</sub>  = 50<br>75  | ± 7 to 50                                                        | 100 @ 5, 100                                               | 10. 0.1                    | ± 3.5, 70        | 1200                  | 3, 20                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | 1          | 1 1        | Π     |     |   |

| CLC402                         | 14-Bit Accurate<br>Low Offset and Drift     | A <sub>v</sub>  =1<br>260       | A <sub>v</sub>  =2<br>190   | A <sub>v</sub>   = 8<br>85  | ± 1 to 8                                                         | 80 @ 5, 100                                                | 25, 0.0025                 | ± 3.5, 55        | 800                   | 0.5, 3.0                          | $R_L = 100\Omega$<br>$V_m = \pm 5V$                                      | 1          | 1 1        | Π     |     |   |

| CLC404                         | High Full-Power BW<br>Low Power, High Slew  | A <sub>v</sub>  =2<br>165       | A <sub>v</sub>  =6<br>175   | A <sub>v</sub>   = 20<br>60 | + 2 to + 21<br>- 1 to - 20                                       | 165 @ 5, 100                                               | 10, 0.2                    | ± 3.3, 70        | 2600                  | 2.0, 30                           | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | 1          | 1 1        | Π     |     |   |

| CLC406                         | Low Cost<br>Low Power                       | A <sub>y</sub>  =2<br>180       | A <sub>v</sub>  =6<br>160   | A <sub>v</sub>  = 10<br>100 | ± 1 to 10                                                        | 130 @ 5, 100                                               | 12, 0.05                   | ± 2.7, 70        | 1500                  | 2, 30                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | 1          | 1 1        | Π     |     |   |

| CLC409                         | Very<br>Wideband                            | A <sub>v</sub>  =2<br>350       | A <sub>v</sub>   = 6<br>150 | A <sub>v</sub>  = 10<br>100 | ± 1 to 10                                                        | 110 @ 5, 100                                               | 8, 0.1                     | ± 3.5, 70        | 1200                  | 0.5, 25                           | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | <b>√</b>   | 1 1        | Π     |     |   |

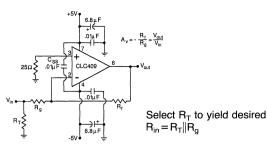

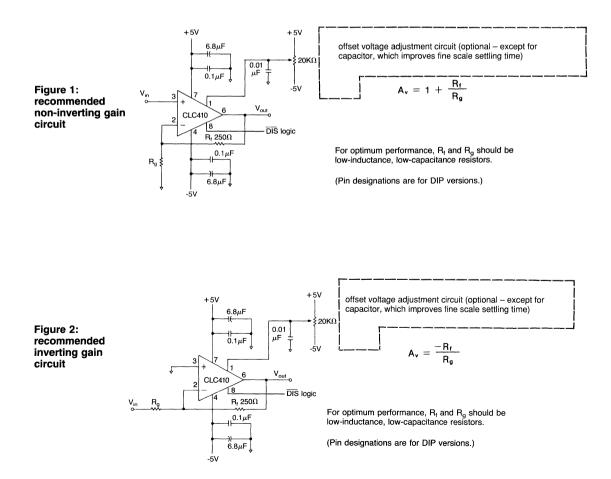

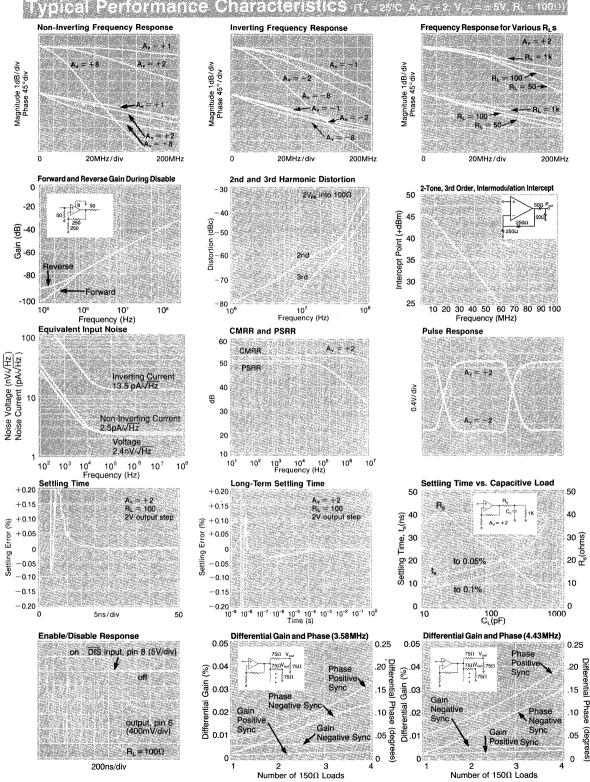

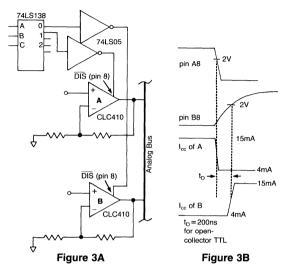

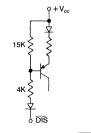

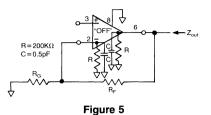

| CLC410                         | High-Speed Video<br>Op Amp with Disable     | A <sub>v</sub>  =1<br>220       | A <sub>v</sub>   ⇒ 2<br>200 | A <sub>v</sub>   = 8<br>60  | ± 1 to 8                                                         | 50 @ 5, 100                                                | 12, 0.05                   | ± 3.5, 70        | 700 (NI)<br>1600 (IN) | 2, 20                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | 1          | 1 1        |       |     |   |

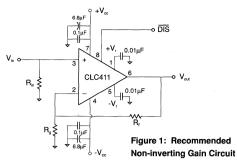

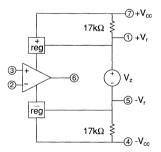

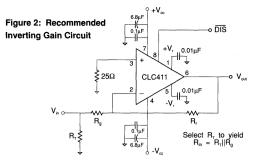

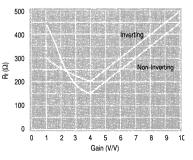

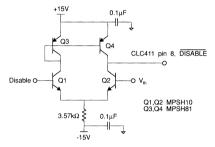

| CLC411                         | High-Speed Video<br>Op Amp with Disabler    | A <sub>y</sub>  =1<br>275       | A <sub>v</sub>  =2<br>200   | A <sub>v</sub>  = 10<br>37  | ± 1 to 10                                                        | 75 @ 15, 100                                               | 15, 0.1                    | ± 4.5, 70        | 2300                  | 2, 30                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 15V$                                  | 1          | 1 1        |       |     |   |

| CLC412                         | Dual Amp<br>Low Power                       | A <sub>y</sub>  =2<br>320       |                             |                             | ± 1 to 10                                                        | 105 @ 4, 100                                               | 12, 0.05                   | ± 2.2, 70        | 1300                  | 2, 30                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | 1          | *   *      |       |     |   |

| CLC414                         | Quad Amp<br>Low Power                       | A <sub>y</sub>  =2<br>70        | A <sub>v</sub>   = 6<br>90  | A <sub>v</sub>  = 10<br>60  | ± 1 to 10                                                        | 55 @ 5, 100                                                | 16, 0.1                    | ± 2.8, 70        | 1000                  | 2, 30                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | √ .        | V V        |       |     |   |

| CLC415                         | Quad Amp<br>High Speed                      | A, =2<br>180                    | A <sub>v</sub>  =6<br>160   | A <sub>v</sub>  = 10<br>140 | ± 1 to 10                                                        | 120 @ 5, 100                                               | 12, 0.1                    | ± 2.6, 70        | 1500                  | 2, 20                             | $R_L = 100\Omega$<br>$V_{cc} = \pm 5V$                                   | <b>√</b> · | VV         | Π     |     | l |

### Operational Amplifiers (typical specifications, +25°C)

| Model <sup>1,3</sup> | Key Features                                                     | - 248 8                    | andwidth                    | (MH-)                                | Gain Range                 | Full Power BW              | Settling Time | Output   | Slew Rate | Input Offset     | Test                                                                  |     |          | Ver | sion | IS <sup>1</sup> |   |

|----------------------|------------------------------------------------------------------|----------------------------|-----------------------------|--------------------------------------|----------------------------|----------------------------|---------------|----------|-----------|------------------|-----------------------------------------------------------------------|-----|----------|-----|------|-----------------|---|

| NOUEI                | Rey Features                                                     | - 505 6                    | andwidth                    | (19112)                              | (Av = V₀/Vı)               | (MHz@V <sub>pp</sub> , RL) | (nsec, %)     | (V, mA)  | (V/µsec)  | Drift (mV,µV/°C) | Conditions                                                            | J   | E        | I K | М    | 8               | Ŀ |

| CLC 420              | Voltage Feedback<br>Low Gain                                     | A <sub>v</sub>  =1<br>300  | A <sub>v</sub>  =2<br>100   | A <sub>v</sub>  =5<br>25             | ± 1 to 10                  | 40@5, 100                  | 18, 0.01      | 3.2, 70  | 1100      | 0.5, 4/1, 3      | $\begin{array}{l} R_{L} \pm 100\Omega \\ V_{CC} = \pm 5V \end{array}$ | 1   | 1        | V   | Τ    | 7               | V |

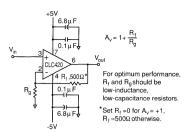

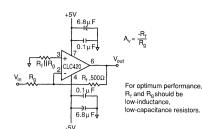

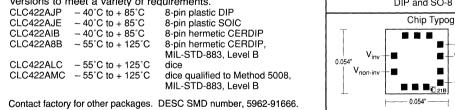

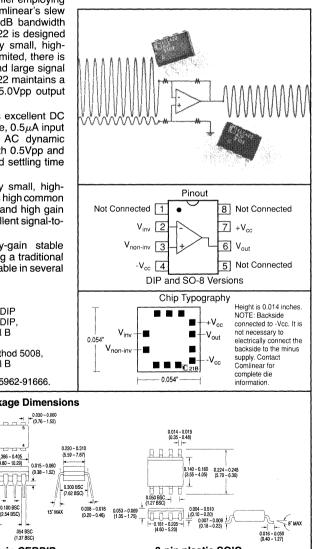

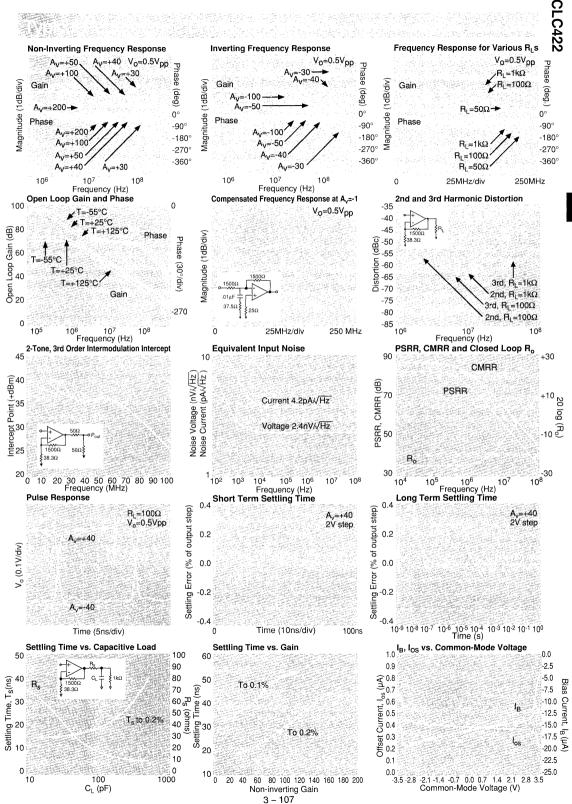

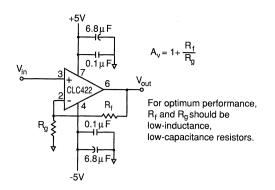

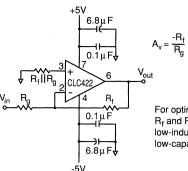

| CLC422               | Voltage Feedback<br>High Gain                                    | A <sub>v</sub>  =30<br>250 | A <sub>v</sub>   =40<br>200 | A <sub>v</sub>  =50<br>120           | ±30 to ±200                | 200@5, 100                 | 17, 0.2       | ±3.8, 70 | 2300      | 0.8, 2           | $\begin{array}{l} R_{L} \pm 100\Omega \\ V_{cc} = \pm 5V \end{array}$ | √ . | √ .      | V   | Ι    | V               | V |

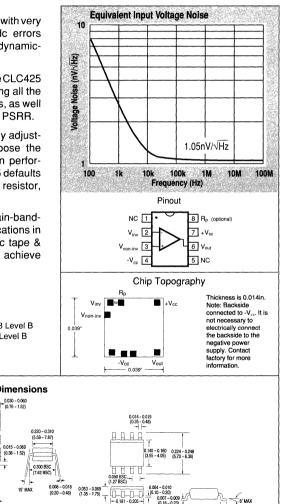

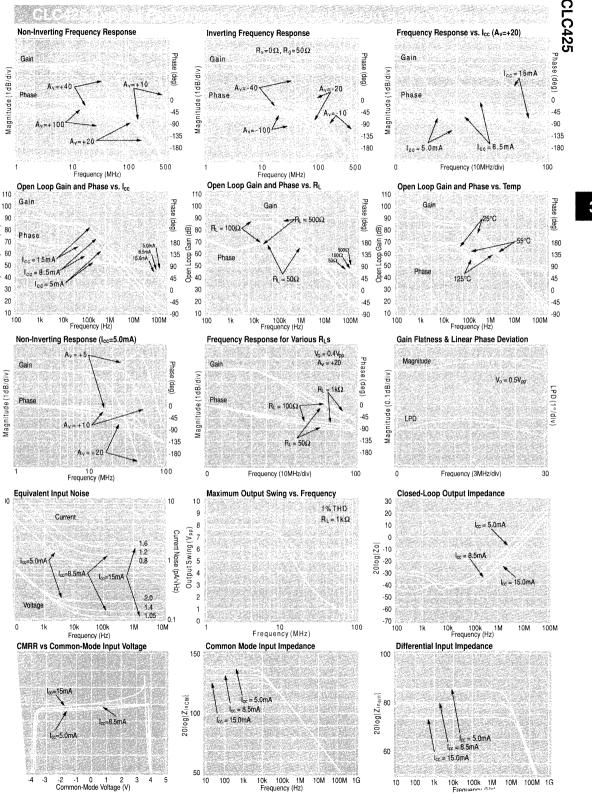

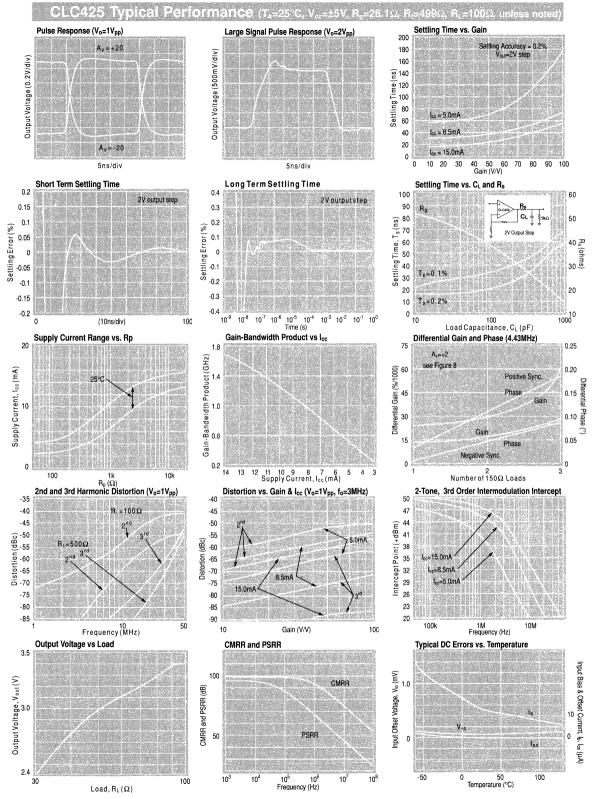

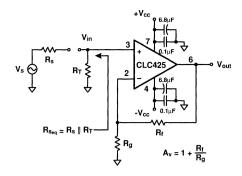

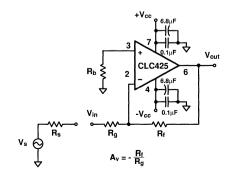

| CLC425               | Ultra Low Noise<br>Wideband Op Amp                               |                            | A <sub>v</sub>   =20<br>85  | A <sub>v</sub>  =40<br>40            | ±10 to ±1000               | TBD                        | 22, 0.1       | 3.4, 90  | 350       | 0.1, 3           | $\begin{array}{l} R_{L} \pm 100\Omega \\ V_{cc} = \pm 5V \end{array}$ | √ · | V        | *   | Τ    | ŀ               | * |

| CLC430               | Low Gain Op Amp<br>with Disable                                  | A <sub>v</sub>   =1<br>48  | A <sub>v</sub>   =2<br>55   | A <sub>v</sub>   =10<br>19           | ± 1 to 10                  | 27@10, 100                 | 35, 0.05      | ±8, 85   | 2000      | 2, 25            | RL ± 100Ω<br>Vcc = ±15                                                | √ . | 1        | V   | Τ    | V               | V |

| CLC501               | Clamped Output<br>Insec Overload Recovery                        | A <sub>v</sub>  =8<br>165  | A <sub>v</sub>  =20<br>120  | A <sub>v</sub>  =32<br>80            | + 7 to + 50<br>- 1 to - 50 | 80@5, 100                  | 12, 0.05      | ±3.5, 70 | 1200      | 1.5, 10          | RL ± 100Ω<br>Vcc = ±5V                                                | 1   | √ ·      | V   | Τ    | V               | Γ |

| CLC502               | Clamped Output, Low<br>Offset, 14-bit Settling                   | A <sub>v</sub>   =1<br>190 | A <sub>v</sub>  =2<br>150   | A <sub>v</sub>  =8<br>75             | + 1 to 8                   | 65@5, 100                  | 25, 0.0025    | ±3.5, 55 | 800       | 0.5, 3.0         | RL ± 100Ω<br>Vcc = ±5V                                                | 1   | <u>ا</u> | V   | Τ    | V               |   |

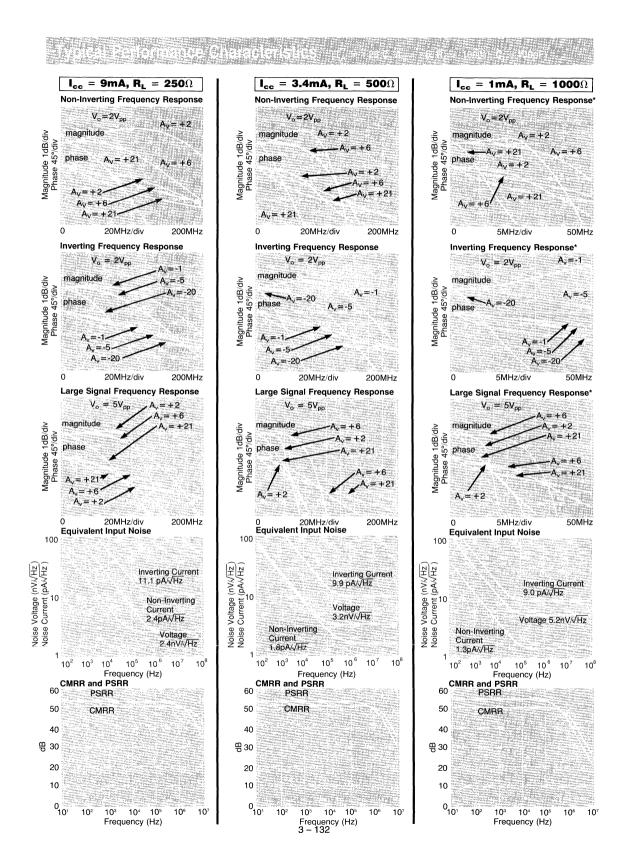

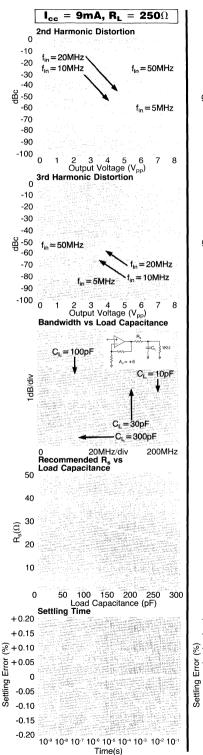

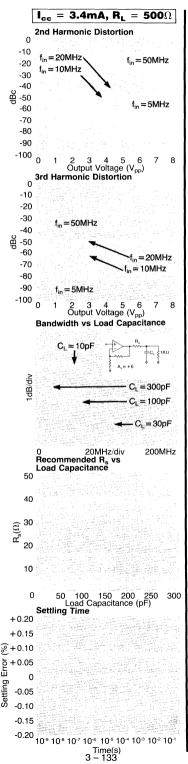

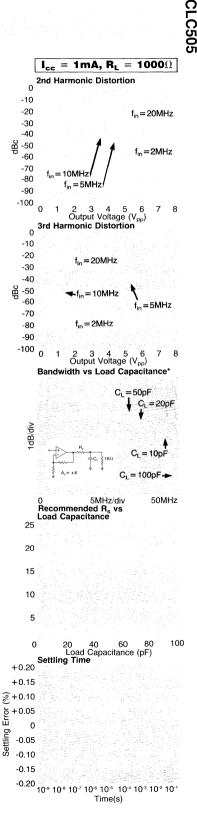

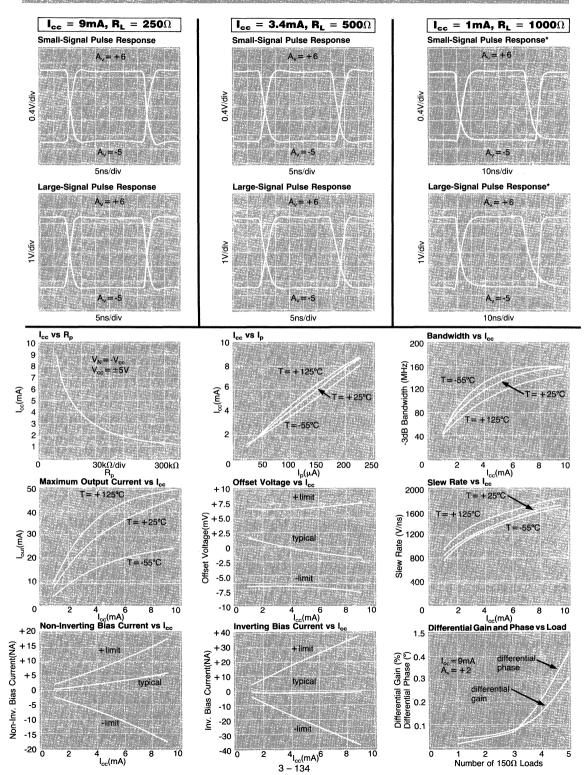

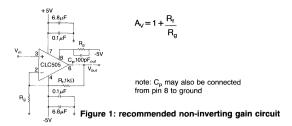

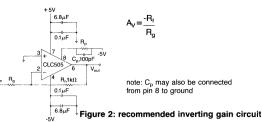

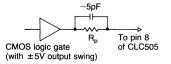

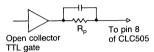

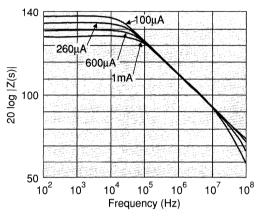

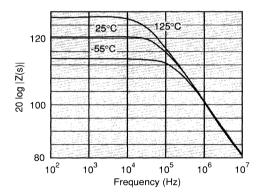

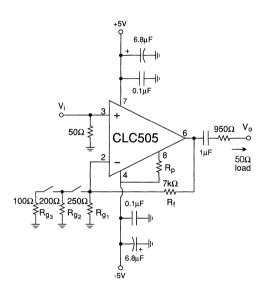

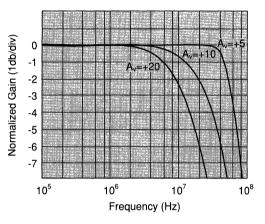

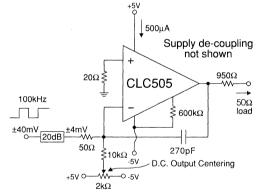

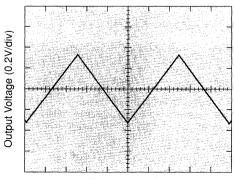

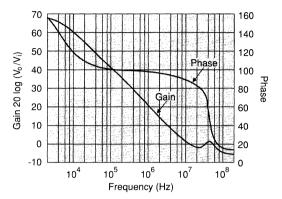

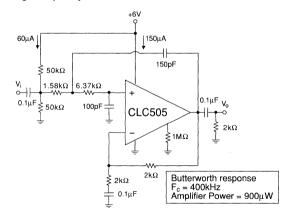

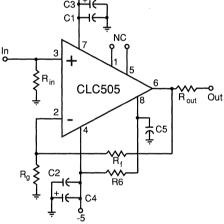

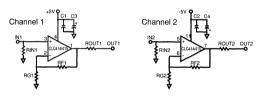

| CLC505               | Very Low Pro-<br>grammable Supply Current/<br>Power (10mW-100mW) | Av   =6<br>50<br>Icc1mA    | Av   =6<br>100<br>Icc3.4mA  | A <sub>v</sub>   =6<br>150<br>Icc9mA | + 2 to + 21<br>- 1 to - 20 | 80@5, 500                  | 14, 0.05      | ±3.3, 25 | 1200      | 3.0, 40          | $l_{cc} = 3.4 \text{mA}$<br>$V_{cc} = \pm 5 \text{V}$                 | √ . | V        | V   |      | V               | V |

### **Operational Amplifiers (typical specifications, +25°C)**

### High Power Amplifiers (typical specifications, +25°C, $R_L = 50\Omega$ )

| Model <sup>1,3</sup> | Key Features                     | ~ 3dB Bandwidth<br>(MHz) | Large Signal<br>Bandwidth<br>(MHz@Vpp) | 10dBm    |          | 24dBn    | on (dBc)<br>n (10V <sub>PP</sub> )<br>100MHz | Rise Time<br>(nsec) | Input Offset<br>Drift (mV,µV/°C) | μV/°C)         Range<br>(V/V)         Range           35         + 5 to + 80         25Ωto20 | Rout<br>Range (Ω) | Output<br>(V, mA) |              |   | ons <sup>1</sup> |

|----------------------|----------------------------------|--------------------------|----------------------------------------|----------|----------|----------|----------------------------------------------|---------------------|----------------------------------|----------------------------------------------------------------------------------------------|-------------------|-------------------|--------------|---|------------------|

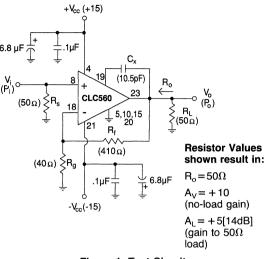

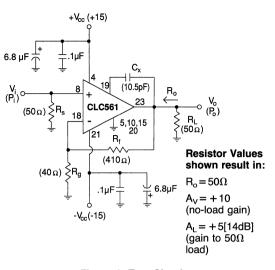

| CLC560               | High-power,<br>adjustable output | 215                      | 120@10Vpp(24dBm)                       | -60/ -62 | 54/44    | 46/38    | -33/ -25<br>(50MHz)                          | 1.6                 | 2.0, 35                          | + 5 to + 80                                                                                  | 25Ωto200Ω         | ± 10V, 200mA      | V            |   | 1                |

| CLC561               | impedence                        | 215                      | 150@10Vpp(24dBm)                       | 59/62    | -35/ -49 | -50/ -41 | -40/ -30                                     | 1.5                 | 2.0, 35                          | + 5 to + 80                                                                                  | 25Ωto200Ω         | ± 10V, 200mA      | $\checkmark$ | Τ | V                |

### Variable Gain Amplifiers (typical specifications, + 25° C)

|   | Model <sup>1,3</sup> | Key Features                     | -3(dB) Bandy   | width (MHz)   | Gain Adjust | Signal            | Fuli Power BW             | Settling Time | Output   | Slew Rate | Output Offset    |   | 1 | Vers | ion |   | Г |

|---|----------------------|----------------------------------|----------------|---------------|-------------|-------------------|---------------------------|---------------|----------|-----------|------------------|---|---|------|-----|---|---|

|   |                      |                                  | Signal Channel | Control Chan. | Range (dB)  | Non-Linearity (%) | (MHz@V <sub>PP</sub> ,RL) | (nsec, %)     | (V,mA)   | (V/µsec   | Drift (mV₁µV/°C) | J | E | 1 1  | ( M | 8 | L |

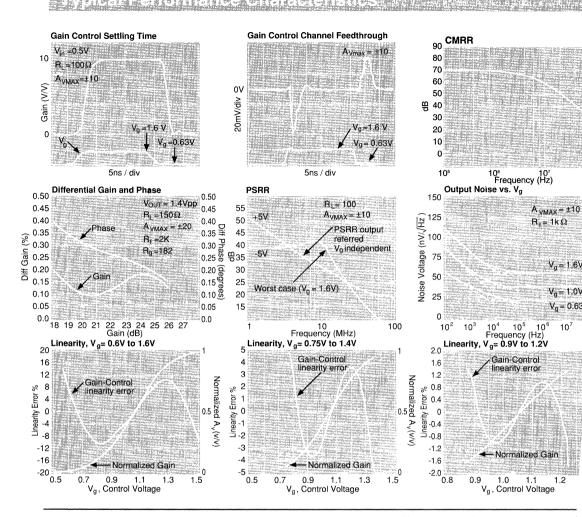

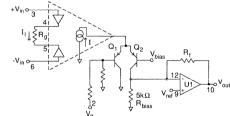

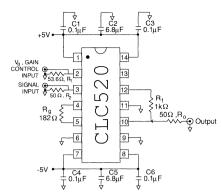

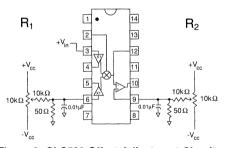

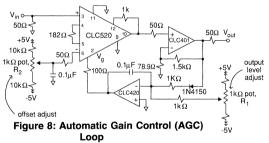

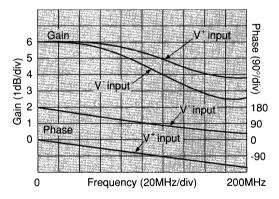

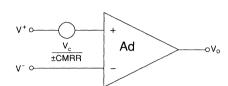

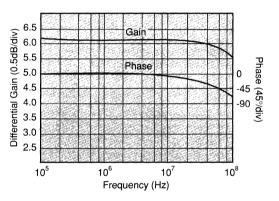

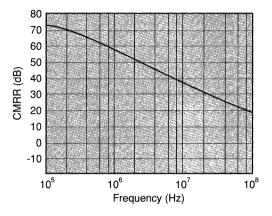

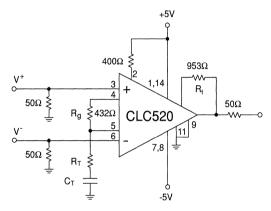

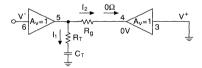

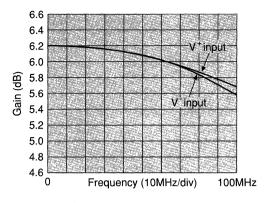

|   | CLC520               | Voltage Controlled<br>Gain (AGC) | 160            | 100           | - 40        | 0.04              | 140 @ 4, 100              | 12, 0.1       | ±3.5, 70 | 2000      | 40, 100          | 1 | 1 | ·    |     | ŀ |   |

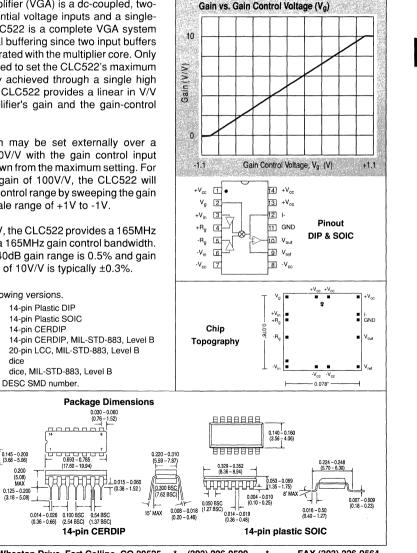

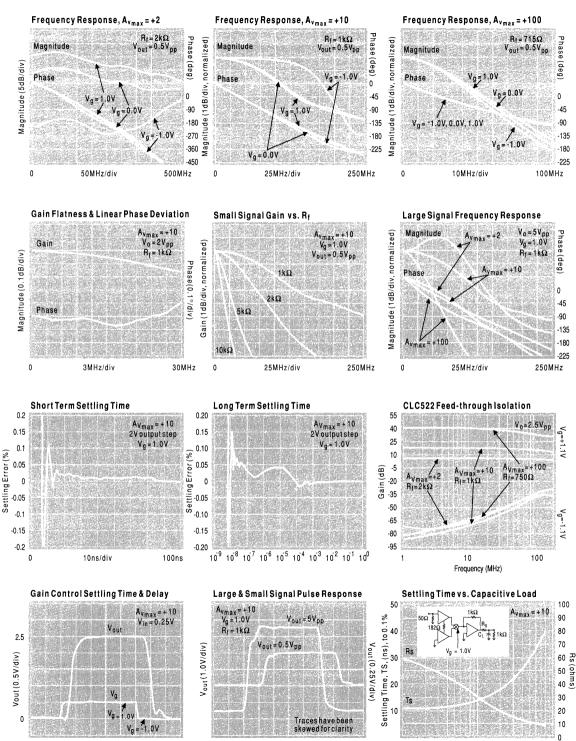

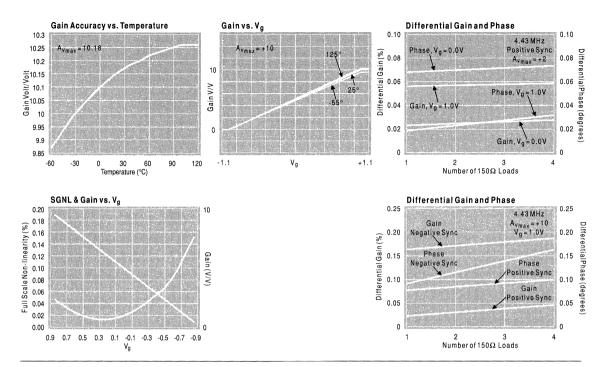

| ≯ | CLC522               | Variable Gain<br>Amplifier (VGA) | 165            | 165           | - 40        | 0.04              | 150 @ 5, 100              | 18, 0.1       | ±4, 70   | 2000      | 25, 100          | 1 | V | ·    |     | * | • |

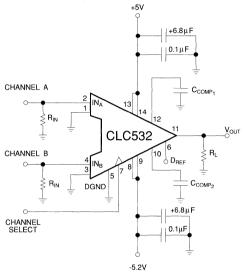

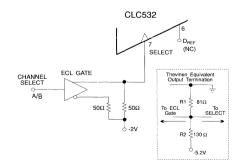

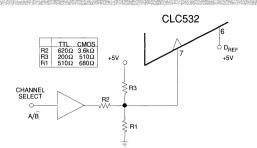

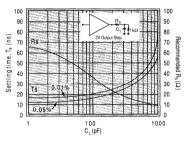

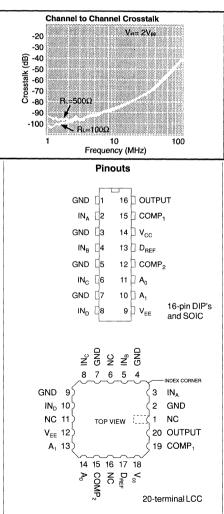

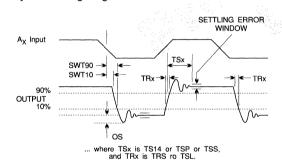

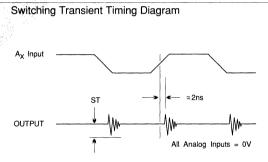

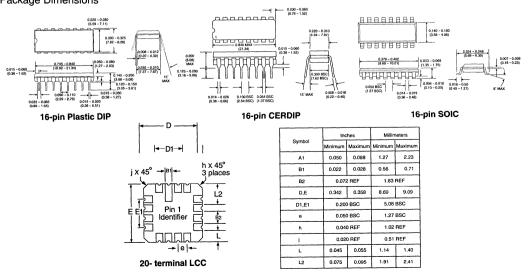

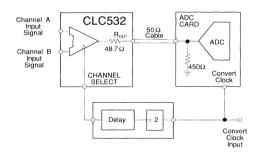

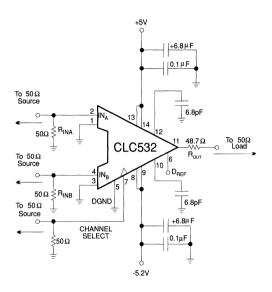

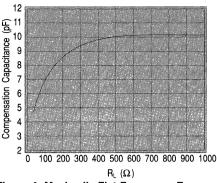

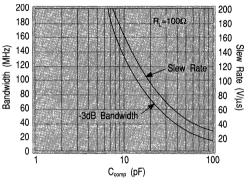

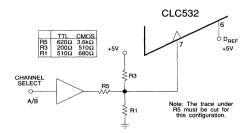

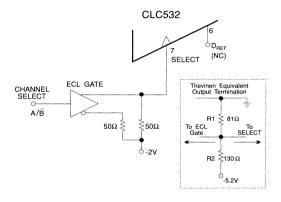

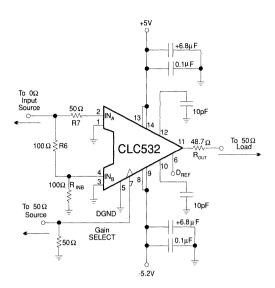

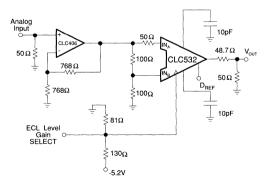

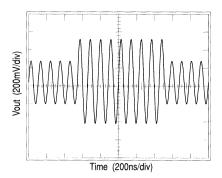

### Analog Multiplexers (typical specifications, +25°C)

| Model <sup>1, 3</sup> | Channels | Switching<br>Speed<br>(ns) | Input<br>Voltage<br>Range | Crosstalk<br>Rejection<br>(dB) | Settling<br>Time to<br>0.01% | Settling<br>Time to<br>0.0025% | 2nd Harmonic<br>Distortion<br>(dBc) | 3rd Harmonic<br>Distortion<br>(dBc) | Digital<br>Interface | Features              | J            | E                       | 1            | /ers | T | s'<br>3 L |

|-----------------------|----------|----------------------------|---------------------------|--------------------------------|------------------------------|--------------------------------|-------------------------------------|-------------------------------------|----------------------|-----------------------|--------------|-------------------------|--------------|------|---|-----------|

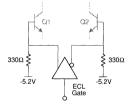

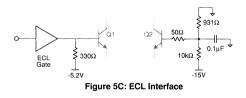

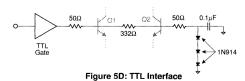

| CLC 532               | 2:1      | 6                          | ±3.4V                     | - 80                           | 17ns                         | 35ns                           | - 80                                | - 86                                | TTL/ECL              | Buffered input/output | $\checkmark$ | $\overline{\mathbf{A}}$ | $\checkmark$ | Т    | 1 | П         |

|                       | 4:1      | 7                          | ±3.4V                     | - 80                           | 17ns                         |                                | - 80                                | - 86                                | TTL/ECL              | Buffered input/output | $\checkmark$ | $\checkmark$            | $\checkmark$ |      | T |           |

|                     | Model <sup>1, 3</sup> | Resolution<br>(Bits) | Sampling<br>Rate | Input<br>Voltage                                | Differential<br>Non-Linearity | Spurious Free Signal<br>Range SFSR (dB) | SNR (excl.<br>harmonics) | Dynamic<br>Test                                                   | Digital<br>Inter- | Power<br>Dissipa- | Architecture           | Features                         | 1 | Ver | sior | 1S1 |   |

|---------------------|-----------------------|----------------------|------------------|-------------------------------------------------|-------------------------------|-----------------------------------------|--------------------------|-------------------------------------------------------------------|-------------------|-------------------|------------------------|----------------------------------|---|-----|------|-----|---|

| _                   |                       | (Bits)               | (MSPS)           | Range                                           | (LSB's)                       | hange or on (ub)                        | (dB)                     | Conditions                                                        | face              | tion (W)          |                        |                                  | с | J   | 1 1  | < м | 8 |

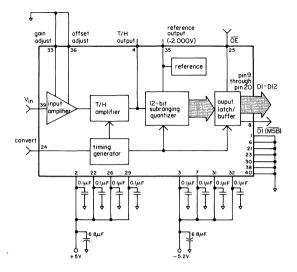

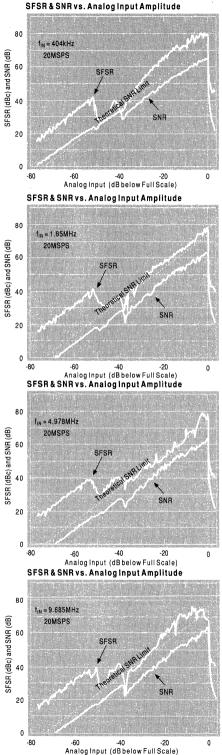

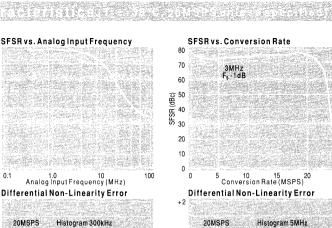

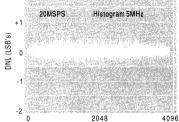

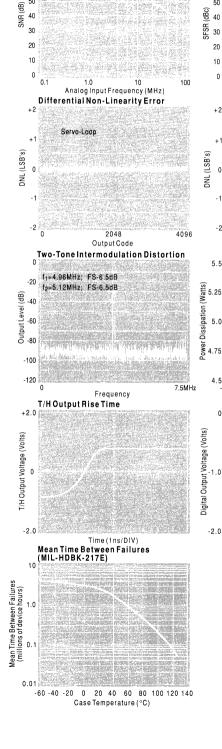

|                     | CLC922B               | 12                   | dc to 10         | ±1V                                             | 0.35                          | 66.6                                    | 66.6                     | F <sub>s</sub>                                                    | TTL               | 4.1               | ±5V<br>Sub-system      |                                  |   |     | V    |     | V |

| _                   | CLC925B               | 12                   | dc to 10         | 2V <sub>pp</sub> over a<br>-2V to + 2V<br>range | 0.35                          | 66.8                                    | 66.6                     | F <sub>s</sub> =10MSPS<br>F <sub>in</sub> =4.996MHz<br>FS =-1dB   | TTL               | 4.2               | Complete<br>sub-system | Internal<br>T/H and<br>reference |   |     | V    | T   | V |

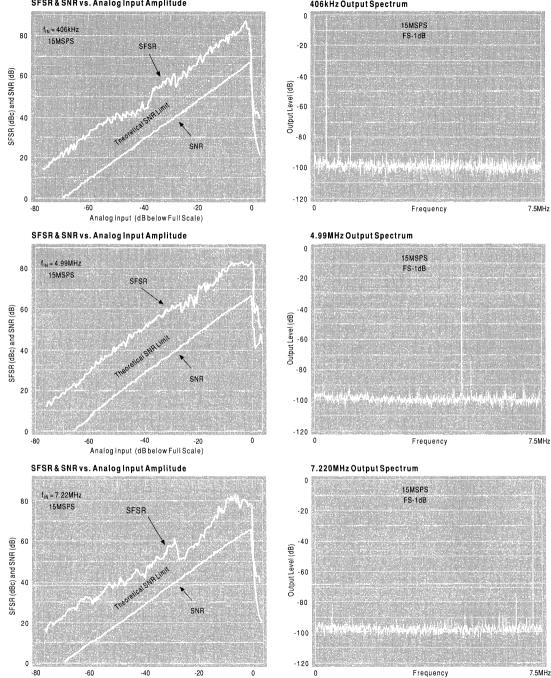

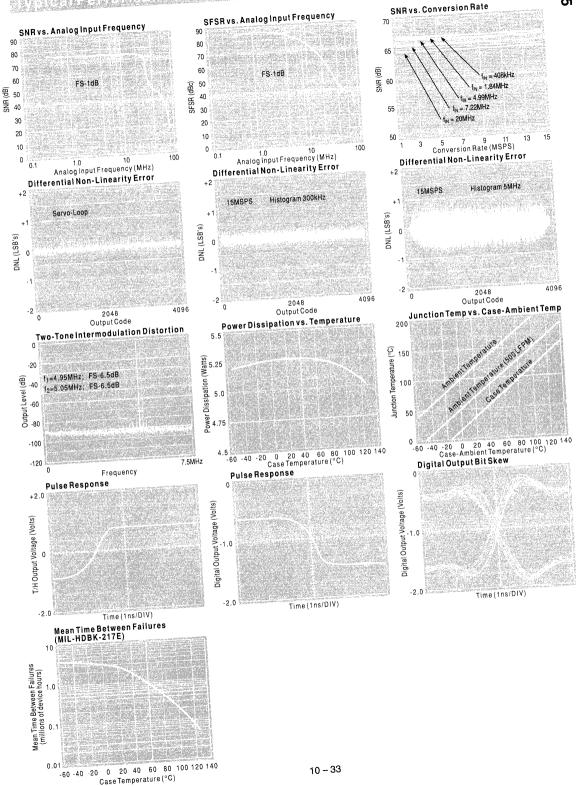

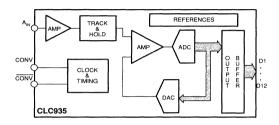

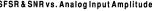

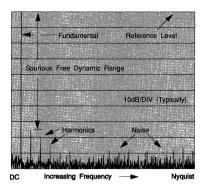

| _                   | CLC935                | 12                   | dc to 15         | ±1V                                             | 0.7                           | 75.0                                    | 66.3                     | F <sub>s</sub> =15MSPS<br>F <sub>in</sub> =7.227MHz<br>FS =-1dB   | ECL               | 5.2               | Complete<br>Sub-system | has gain<br>and offset<br>adjust | Ą |     |      |     | * |

|                     | CLC936                | 12                   | dc to 20         | ±1V                                             | 0.7                           | 65.0                                    | 64.0                     | F <sub>s</sub> =20MSPS<br>F <sub>in</sub> =9.685MHz<br>FS =-1dB   | ECL               | 5.4               | Complete<br>Sub-system |                                  | V |     |      | T   | * |

| 9 <sup>3</sup><br>≯ | CLC937                |                      | dc to 25.6       |                                                 |                               | 65.0                                    | 62.0                     | F <sub>s</sub> =25.6MSPS<br>F <sub>in</sub> =9.685MHz<br>FS = 1dB |                   | 6.4               |                        | Internal<br>T/H and<br>reference | 1 |     | T    |     |   |

| 4                   | CLC950                | 12                   | dc to 25.6       | ±1V                                             | 1.0                           | 65.0                                    | 64.0                     | F <sub>s</sub> =25.6MSPS<br>F <sub>in</sub> =9.685MHz<br>FS = 1dB | TTL/ECL           | 1.9               | Complex<br>Monolithic  | Internal<br>T/H                  |   | √.  | V    | Τ   | V |

### Analog to Digital Converters (typical specifications, + 25°C)

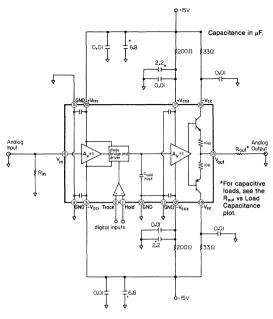

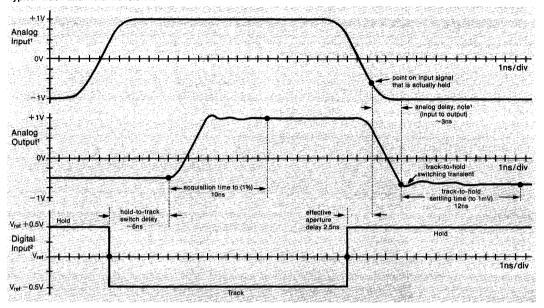

### Track + Hold Amplifiers (typical specifications, + 25° C, $R_L = R_S = 50\Omega$ , $V_{cc} = \pm 15V$ )

| Model <sup>1,3</sup>   | H-to-T<br>Acquistion Time, | T-to-H<br>Settling Time | Effective<br>Aperture | Aperture<br>Jitter     | – 3dB<br>Bandwidth | Slew Rate     | Pedestal<br>Offset | Feedthrough<br>Rejection | Output    | Digital    |   |   | ons |   |

|------------------------|----------------------------|-------------------------|-----------------------|------------------------|--------------------|---------------|--------------------|--------------------------|-----------|------------|---|---|-----|---|

|                        | Tolerance                  | to 1mV (nsec)           | Delay (nsec)          | (psec <sub>rms</sub> ) | (MHz)              | <b>(V/μs)</b> | (mV)               | (dB at 20MHz)            | (± V, mA) | Control    | J | 1 | КМ  | L |

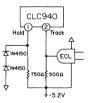

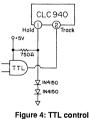

| CLC940<br>FLash-Track™ | 10, 1.0<br>16, 0.1         | 12                      | 2.5                   | 1                      | 150                | 470           | 2                  | 74                       | 2.2, 50   | ECL or TTL |   | 1 | V   | Π |

| CLC942                 | 20, 0.1<br>25, 0.01        | 5                       | - 1.5                 | 1.4                    | 70                 | 300           | 8                  | 78                       | 2.2<br>50 | ECL        |   | V | V   | Π |

NOTES:

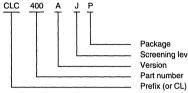

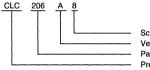

<sup>1</sup>The version designation indicates the temperature range and screening level:

| version | temperature       | screening                          |

|---------|-------------------|------------------------------------|

| C:      | 0°C to + 70°C     | commercial                         |

| J:      | - 40°C to + 85°C  | industrial                         |

| l:      | - 40°C to + 85°C  | industrial: hybrid                 |

| E:      | - 40°C to + 85°C  | commercial SOIC                    |

| K:      | – 55°C to + 125°C | high-reliability industrial hybrid |

| L:      | – 55°C to + 125°C | dice                               |

| M:      | - 55°C to + 125°C | hybrid: high-reliability military  |

| 8:      | – 55°C to + 125°C | MIL-STD-883 compliant              |

<sup>2</sup>CLC100 and CLC104A are non-inverting, CLC102 is inverting gain.

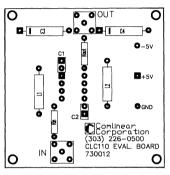

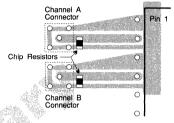

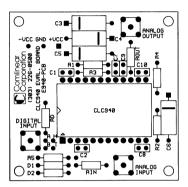

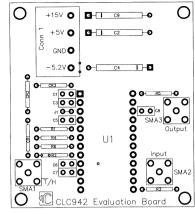

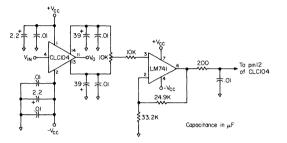

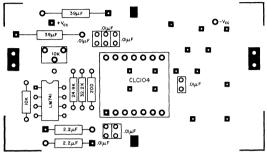

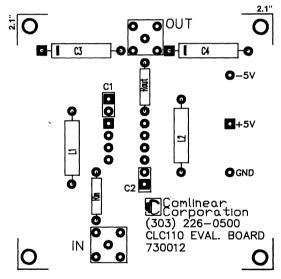

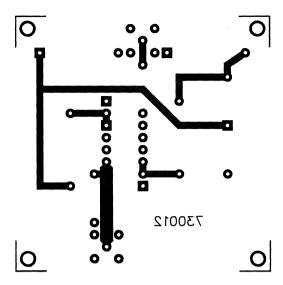

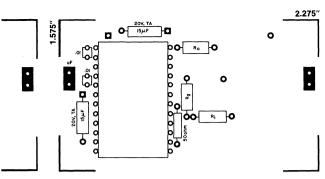

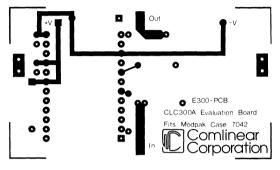

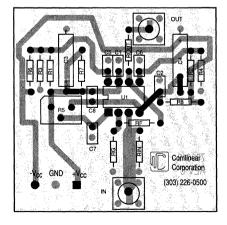

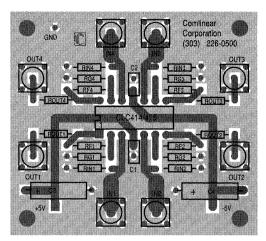

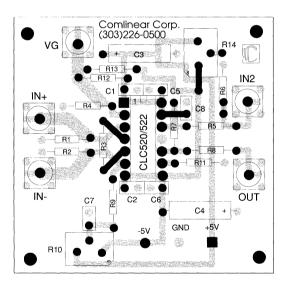

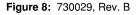

<sup>3</sup>Evaluation boards are available for all hybrid and monolithic integrated circuits. Encased and connectorized versions of the CLC103, CLC203, CLC200, CLC201, CLC220, CLC221, CLC231 and CLC104 are available as well. Contact Comlinear or your local Comlinear representative for details. \*Contact the factory for further information. Indicates new products since 1991 databook.

See the individual product data sheets for details.

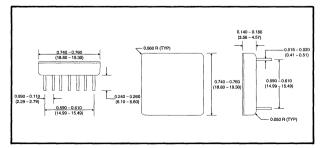

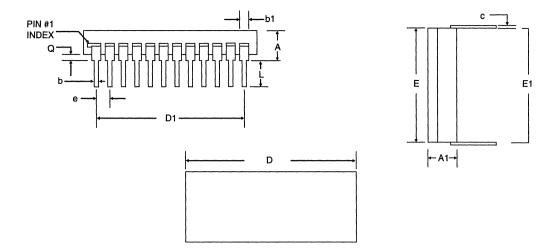

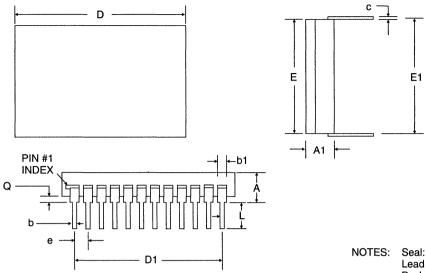

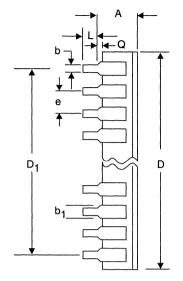

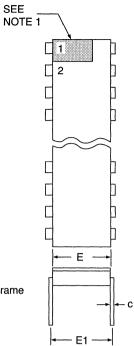

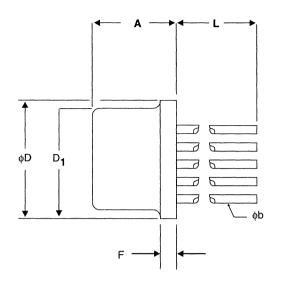

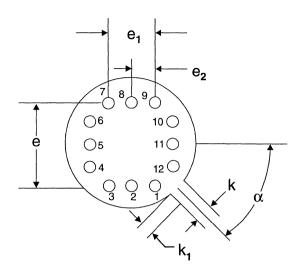

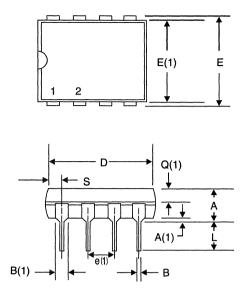

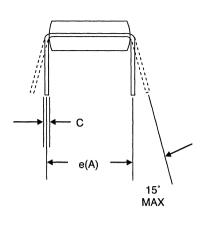

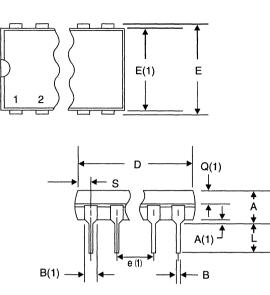

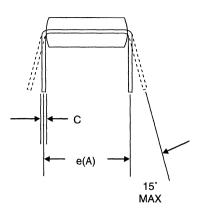

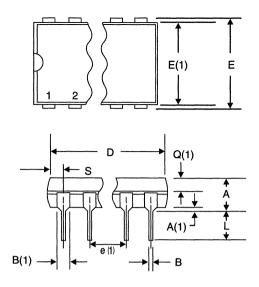

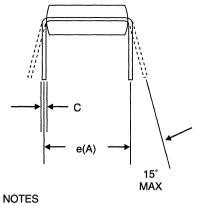

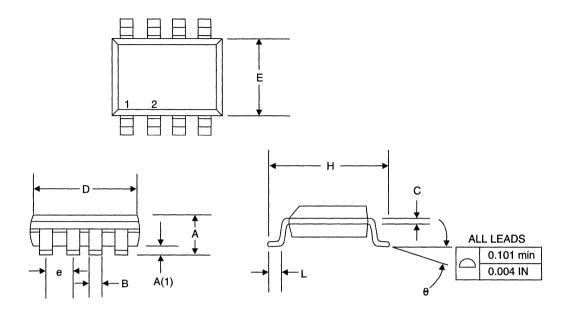

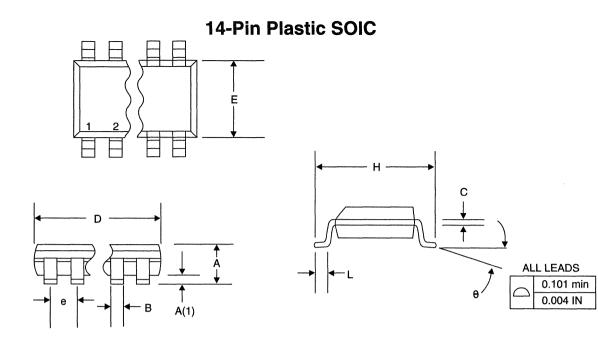

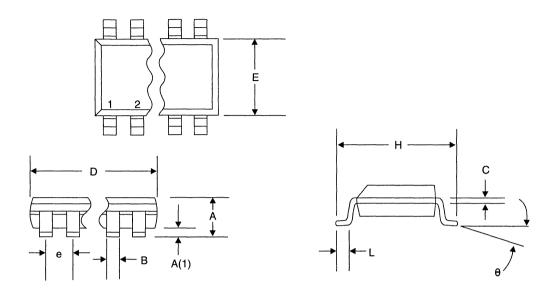

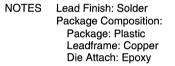

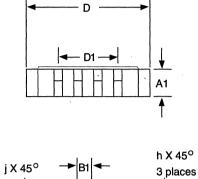

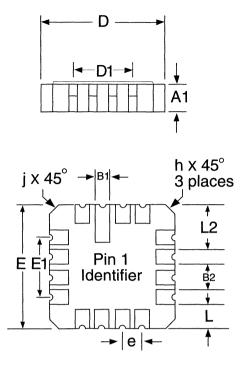

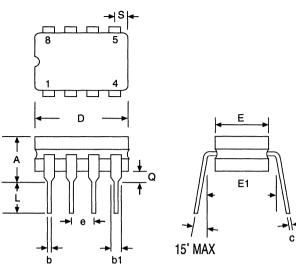

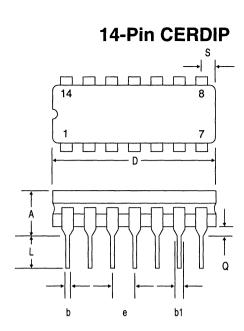

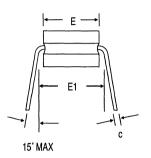

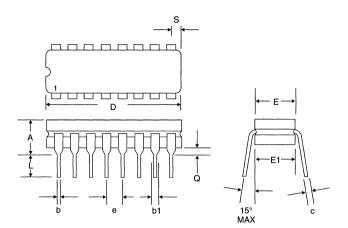

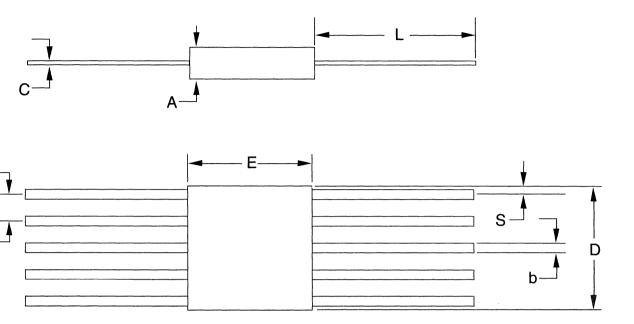

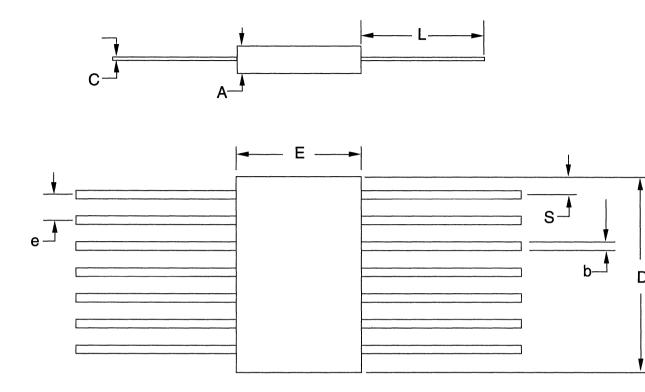

| Package<br>Type                                |      | Dual in Line  |               |             |      |     |              | · · · · · · · · · · · · · · · · · · · |               |              | S  | Surface | e mour         | nt                   |    | TO-8 | Die         |     |     |       |               |

|------------------------------------------------|------|---------------|---------------|-------------|------|-----|--------------|---------------------------------------|---------------|--------------|----|---------|----------------|----------------------|----|------|-------------|-----|-----|-------|---------------|

| Package<br>Material                            |      | Plas          | tic           |             | Cerc | lip |              |                                       | amic<br>Braze | : Side<br>ed | e  | Metal   | 0              | Sma<br>utline        |    |      | CC          | Cei | pak | Metal | Waffle Pack   |

|                                                | 4    | $\mathcal{H}$ | $\mathcal{R}$ |             |      | T   |              | ŗ                                     |               | ŋ            |    |         |                | (SOI(                |    |      |             | c   |     |       |               |

| Number of<br>Pins                              | 8    | 14            | 16            | 8           | 14   | 16  | 8            | 14                                    | 16            | 24           | 40 | 14      | 8              | 14                   | 16 | 16   | 20          | 10  | 14  | 12    |               |

| CLC103<br>CLC104<br>CLC110<br>CLC114<br>CLC115 | V    | $\sqrt[]{}$   |               | V           | V    |     | √            | $\sqrt[]{}$                           |               | V            |    | V       | V              | $\sqrt[n]{\sqrt{1}}$ |    |      | •<br>√      |     |     |       | ~ ~ ~         |

| CLC200<br>CLC201<br>CLC203<br>CLC205<br>CLC206 |      |               |               |             |      |     |              |                                       |               | V            |    |         |                |                      |    |      |             |     |     |       |               |

| CLC207<br>CLC220<br>CLC221<br>CLC231<br>CLC232 |      |               |               |             |      |     |              |                                       |               |              |    |         |                |                      |    |      |             |     |     | イマイ   |               |

| CLC300<br>CLC400<br>CLC401<br>CLC402<br>CLC404 | オオオオ |               |               | √<br>√<br>• |      |     |              |                                       |               | V            |    |         | イイイ            |                      |    |      | √<br>•<br>• |     |     |       | イイイ           |

| CLC406<br>CLC409<br>CLC410<br>CLC411<br>CLC412 | オメメメ |               |               | √<br>•<br>• |      |     | $\checkmark$ |                                       |               |              |    |         | √ √ √ √<br>• √ |                      |    |      | •<br>√<br>• |     |     |       | ~~~<br>~<br>• |

√ Existing Package

• Future Package

1 - 7

|       | Package<br>Type                                          |                           | Dual in Line |    |     |      |     |        |     |                 | S    | Surface | e mour       | nt           |    | TO-8 | Die         |        |              |       |                      |

|-------|----------------------------------------------------------|---------------------------|--------------|----|-----|------|-----|--------|-----|-----------------|------|---------|--------------|--------------|----|------|-------------|--------|--------------|-------|----------------------|

|       | Package<br>Material                                      | I                         | Plast        | ic |     | Cerd | lip | Ce     |     | nic Sid<br>Ized | le   | Metal   | 0            | Sma          |    |      |             | Ce     | rpak         | Metal | Waffle Pack          |

|       |                                                          |                           |              | Y  |     |      | Ţ   |        | ]]] |                 |      |         |              |              |    |      |             | C      |              |       |                      |

|       | Number of<br>Pins                                        | 8                         | 14           | 16 | 8   | 14   | 16  | 8 14   | 1   | 6 24            | 40   | 14      | 8            | 14           | 16 | 16   | 20          | 10     | 14           | 12    |                      |

| 1 – 8 | CLC414<br>CLC415<br>CLC420<br>CLC422<br>CLC425<br>CLC430 | イイイ                       | $\checkmark$ |    | • 1 | •    |     |        |     |                 |      |         | √ √ √<br>√ √ | $\checkmark$ |    |      | √<br>•<br>• |        |              |       | インシン                 |

|       | CLC501<br>CLC502<br>CLC505<br>CLC520                     | $\checkmark$ $\checkmark$ | $\checkmark$ |    | •   | •    |     |        |     |                 |      |         | $\checkmark$ | $\checkmark$ |    | V    | •<br>•<br>• | √<br>√ | $\checkmark$ |       | $\sqrt[n]{\sqrt{1}}$ |

|       | CLC522<br>CLC532<br>CLC533<br>CLC560<br>CLC561           |                           | $\sqrt[]{}$  | γ  |     | •    | •   | √<br>√ |     | $\sqrt[]{}$     |      |         |              | $\sqrt[]{}$  | •  |      | •           |        |              |       | V                    |

|       | CLC922<br>CLC925<br>CLC935<br>CLC936<br>CLC937           |                           |              |    |     |      |     |        |     |                 | イイイイ |         |              |              |    |      |             |        |              |       |                      |

|       | CLC940<br>CLC942                                         |                           |              |    |     |      |     |        |     | $\sqrt[]{}$     |      |         |              |              |    |      |             |        |              |       |                      |

√ Existing Package

• Future Package

# Quality and Reliability Contents

Page

### Section

| Quality and Reliability    | 2 – 3 |

|----------------------------|-------|

| Space Level Products       |       |

| Radiation Data             | 2 – 5 |

| Standard Military Drawings | 2 – 6 |

| Reliability Predictions    |       |

| Thermal Resistance         | 2 –8  |

| ESD                        | 2 – 9 |

| Process Flows              |       |

2

Quality excellence is an approach to business based on understanding the customer's needs, and then striving consistently and efficiently to meet those needs with desired products and services.

Comlinear recognizes that pursuing quality excellence will result in both increased customer and employee satisfaction by achieving higher productivity, improved reliability and increased value.

At Comlinear, quality excellence is implemented through a continuous and committed team approach to quality improvement, from senior management through all employees for all activities of the company.

We elevate quality beyond its typical stature as a military mandated program, and foster an environment where it becomes a pervasive operating attitude. Comlinear's ability to deal with the required elements of a quality program is shown by the continual maintenance of our MIL-STD-1772 facility certification, and our MIL-STD-883 compliant, DESC SMD approved, monolithic and hybrid products.

What makes Comlinear a preferred supplier are our efforts to address the competitive challenge in today's market by focusing on the quality of all of our products and services.

Our commitment to product assurance means that we start with the required systems and then enhance them with the most up-to-date quality assurance techniques available. Tools such as SPC, quality improvement teams, and experimental design are all used in an environment of Total Quality.

Application of these techniques is the responsibility of all managers and employees. These techniques, and the desire for continuous quality improvement, are found in areas ranging from accounting, research and development, and computer services to manufacturing processes and shipment.

The Quality Assurance group supports these efforts by providing technical resources in quality engineering for failure analysis, reliability monitoring, and process improvement. Furthermore, quality levels in manufacturing are continually measured and the information is supplied to the responsible managers. Comlinear will be pursuing assessment and certification to the International Organization for Standardization (ISO), specifications 9000 and 9001. This effort will solidify Comlinear's commitment to fulfilling customer needs and achieving product and service excellence.

### **PRODUCTS AND TECHNOLOGIES**

Comlinear's hybrid circuit manufacturing is located in our MIL-STD-1772 certified production line in Fort Collins, Colorado. Our capabilities include high density thin film substrate fabrication incorporating high precision, high stability tantalum nitride resistors, gold metalization, and alumina substrates. Monolithic microcircuits are fabricated in the U.S.A. using a high speed complementary bipolar integrated circuit process. This combination has demonstrated an actual failure rate for ICs of less than 1.0 FIT in lifetesting.

Both monolithic and hybrid products are available as MIL-STD-883, industrial or commercial levels. DESC SMDs are available for most of our catalog hybrid and monolithic products. Our monolithic products are also available as MIL-STD-883, S (space) level compliant. Though our hybrid products can be processed to selected K (space) level criteria, the final product would not be compliant or certified to MIL-STD-883 or MIL-M-38534, K level.

### ENVIRONMENTAL IMPACT/SAFETY AWARENESS

Comlinear is actively pursuing the elimination of ozone depleting substances (ODS) in its manufacturing processes and is persuading its suppliers to comply with the Montreal Protocol and all U.S Federal regulations.

The flammability rating of commercial, plastic DIP, monolithic products is 94V-0 of the UL-94 Flame Class; this rating is subject to change without notification.

The following section outlines the various flows for both the hybrid and the monolithic product lines and provides additional reliability data.

# SPACE LEVEL PRODUCTS

Comlinear has the expertise, product lines and demonstrated reliability to support your space-based systems. In addition, we have the experience and program management necessary to meet the unique demands of processing components to space level MIL-STD-883 or custom flows.

The monolithic product lines have been designed for the robust, reliable assembly and high radiation tolerance necessary for success in the space system environment. Also, a mono-metallic gold wire bonding system is used for superior dependability.

Recognizing the special nature of space programs and the impact of component performance on system capability, we are fully prepared to provide either our standard S Level screening or full custom processing flows to suit your application requirements. Hybrid products can be processed to selected K (space) level criteria, but the final product would not be compliant or certified to MIL-STD-883 or MIL-M-38534, K level. Contact Comlinear for specific information.

Radiation testing has been completed on several Comlinear products at different levels. Our complementary bipolar IC process, for instance, has shown radiation tolerance up to one megarad total dose.

Neutron Total Part Package Date Dose Irrad. Dose Number Type Quantity Code Rate **Result Summary** (neutron/cm<sup>2</sup>) (krads) CLC205 TO-8 5+1Control 8931 None 50, 100 126 rad Devices withstood radiation 300, 1000 (Si)/sec to 1Mrad (Si) with little degradation. CLC220 3.36 x 1012 TO-8 4+1Control 8508 100.300 Unknown No change in ac 500, 1000 characteristics. Slight change in dc bias characteristics. CLC231 1.2 x 1012 None Slight change in dc operating TO-8 4 None 3.2 x 10<sup>12</sup> characteristics and distortion. 9.9 x 10<sup>12</sup> No change in gain and 25 x 10<sup>12</sup> bandwidth. 36 x 10<sup>12</sup> Ceramic CLC400 Controls 8817 None 10.30.100 140 rad Negligible degradation to side-brazed (.054"x.054" 1000 krad specification. 300, 1000 (Si)/sec DIP TYP die size) Should meet specifications to 3000krad. 1.85 x 10<sup>12</sup> CLC401 Very little change in the small Ceramic None None side-brazed (.054"x.054" signal frequency response TYP die size) DIP over a wide gain range. 570 rad No degradation of test limits CLC401 4 9136 None 10, 30, 50 Ceramic (.039"x.039" side-brazed up to 100 krads. 100 (Si)/min TYP die size) DIP 2 5.10.15 CLC501 50 rad/hr No degradation of gain at all: Plastic DIP None 20, 25 slight degradation of bandwidth at initial radiation exposure only. CLC925 2 0.5, 1, 1.5 Unknown Performance is virtually Ceramic None side-brazed 2, 5, 10, 20 constant from 0 to 56 krad DIP 38, 40, 50 total dose. Any trend versus total dose is obscured by test 56 repeatability.

**Radiation Test Data Summary**<sup>®</sup>

\*Detail Reports Available

Date: 1/93

2 – 5

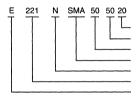

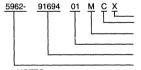

# Standardized Military Drawings (SMD)

Comlinear is involved in and supports a drawing (detail specification) standardization program administered by the Defense Electronics Supply Center (DESC). This program covers all Comlinear products compliant to MIL-STD-883 paragraph 1.2.1, MIL-M-38510 and MIL-H-38534 for monolithic and hybrid devices.

The following listing identifies those models which have DESC (SMD) approval or are in process. Comlinear will, upon device qualification, apply for and seek SMD approval of all products to be compliant to military standards.

Contact Comlinear for new releases or any models currently in-process which are not listed herein.

| SMD                                                                              | CLC Part                                                 |

|----------------------------------------------------------------------------------|----------------------------------------------------------|

| Number                                                                           | Number                                                   |

| 5962-89594<br>5962-89858<br>5962-89910<br>5962-89911<br>5962-89970               | CLC231<br>CLC206<br>CLC200<br>CLC220<br>CLC220<br>CLC400 |

| 5962-89973                                                                       | CLC401                                                   |

| 5962-89974                                                                       | CLC501                                                   |

| 5962-89975                                                                       | CLC110                                                   |

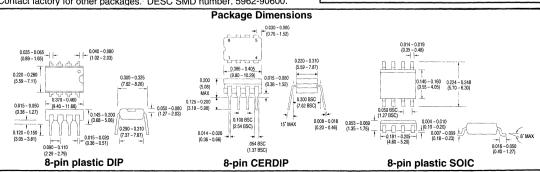

| 5962-90600                                                                       | CLC410                                                   |

| 5962-90756*                                                                      | CLC560                                                   |

| 5962-90833<br>5962-90835<br>5962-90836<br>5962-90925<br>5962-90925<br>5962-90977 | CLC201<br>CLC205<br>CLC221<br>CLC500<br>CLC207           |

| 5962-90993<br>5962-90994<br>5962-90995<br>5962-91665<br>5962-91666*              |                                                          |

| 5962-91693                                                                       | CLC414                                                   |

| 5962-91694                                                                       | CLC520                                                   |

| 5962-91743                                                                       | CLC502                                                   |

| 5962-91758                                                                       | CLC420                                                   |

| 5962-92004                                                                       | CLC406                                                   |

| 5962-92030                                                                       | CLC430                                                   |

| 5962-92033                                                                       | CLC402                                                   |

| 5962-92034                                                                       | CLC409                                                   |

| 5962-92035 <sup>*</sup>                                                          | CLC532                                                   |

| 5962-92039 <sup>*</sup>                                                          | CLC935                                                   |

| 5962-92339                                                                       | CLC114                                                   |

| 5962-93055*                                                                      | CLC415                                                   |

| CLC Part | SMD                     |

|----------|-------------------------|

| Number   | Number                  |

| CLC110   | 5962-89975              |

| CLC114   | 5962-92339              |

| CLC200   | 5962-89910              |

| CLC201   | 5962-90833              |

| CLC205   | 5962-90835              |

| CLC206   | 5962-89858              |

| CLC207   | 5962-90977              |

| CLC220   | 5962-89911              |

| CLC221   | 5962-90836              |

| CLC231   | 5962-89594              |

| CLC232   | 5962-91665              |

| CLC400   | 5962-89970              |

| CLC401   | 5962-89973              |

| CLC402   | 5962-92033              |

| CLC404   | 5962-90994              |

| CLC406   | 5962-92004              |

| CLC409   | 5962-92034              |

| CLC410   | 5962-90600              |

| CLC414   | 5962-91693              |

| CLC415   | 5962-93055              |

| CLC420   | 5962-91758              |

| CLC422   | 5962-91666*             |

| CLC430   | 5962-92030              |

| CLC500   | 5962-90925              |

| CLC501   | 5962-89974              |

| CLC502   | 5962-91743              |

| CLC505   | 5962-90993              |

| CLC520   | 5962-91694              |

| CLC532   | 5962-92035 <sup>*</sup> |

| CLC560   | 5962-90756 <sup>*</sup> |

| CLC925   | 5962-90995              |

| CLC935   | 5962-92039*             |

\* Release Pending

This listing provides mean time between failure (MTBF) rate prediction analysis, calculated in accordance with MIL-HDBK-217E. The stated values are for MIL-STD-883, B level, H level, or Comlinear M level processed versions. For

monolithic products, the number range of transistors has been shown; these products are achieving a continuous tested FIT (Failures in Time) rate of <1.0 fails per billion device hours.

| Part <sup>1</sup><br>Number                              | MTBF <sup>1</sup><br>(million hours)                                           | Number of<br>Transistors <sup>2</sup>                  | Product<br>Process <sup>3</sup> |

|----------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------|

| CLC103<br>CLC110<br>CLC114<br>CLC115<br>CLC200           | 1.76<br>59.5<br>44.8<br>13.4<br>1.47                                           | < 100<br>< 100<br>< 100                                | H<br>M<br>M<br>H                |

| CLC201<br>CLC203<br>CLC205<br>CLC206<br>CLC207           | 1.30<br>1.68<br>1.77<br>2.06<br>1.77                                           |                                                        | H H H H H                       |

| CLC220<br>CLC221<br>CLC231<br>CLC232<br>CLC232<br>CLC400 | 1.42<br>1.30<br>1.65<br>1.65<br>42.1                                           | < 100                                                  | H<br>H<br>H<br>M                |

| CLC401<br>CLC402<br>CLC404<br>CLC406<br>CLC409           | 51.4<br>56.3<br>75.3<br>88.8<br>70.0                                           | < 100<br>< 100<br>< 100<br>< 100<br>< 100<br>< 100     | M<br>M<br>M<br>M                |

| CLC410<br>CLC411<br>CLC412<br>CLC414<br>CLC415           | 50.3<br>15.7<br>51.7<br>30.9<br>23.2                                           | < 100<br>< 100<br>< 100<br>101 - 300<br>101 - 300      | M<br>M<br>M<br>M                |

| CLC420<br>CLC422<br>CLC425<br>CLC430<br>CLC501           | 90.9<br>56.3<br>59.0<br>20.0<br>40.6                                           | < 100<br>< 100<br>< 100<br>< 100<br>< 100<br>< 100     | M<br>M<br>M<br>M                |

| CLC505⁴<br>CLC520<br>CLC522<br>CLC532<br>CLC533          | 68.4<br>24.7<br>12.2<br>27.8<br>10.8                                           | < 100<br>< 100<br>< 100<br>< 100<br>< 100<br>101 - 300 | M<br>M<br>M<br>M                |

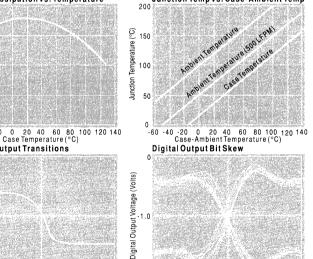

| CLC560<br>CLC561<br>CLC922<br>CLC925<br>CLC935           | 1.64<br>1.64<br>see datasheet plot<br>see datasheet plot<br>see datasheet plot |                                                        | нттт                            |

| CLC936<br>CLC940<br>CLC942                               | see datasheet plot<br>1.15<br>2.22                                             |                                                        | H<br>H<br>H                     |

<sup>1</sup>Based on MIL-STD-883, B Level, H level or our M level versions; per MIL-HDBK-217E; Ground Fixed (GF) at 70° C case still air (hybrid), GF at 25° C ambient still air (monolithic). <sup>2</sup>For CLC hybrid products, the number of transistors is not listed due to further transistor attributes beyond the scope of this listing; these attributes should be discussed with Comlinear personnel directly. <sup>3</sup>H = hybrid; M = monolithic. <sup>4</sup>Rp=33k\Omega

2

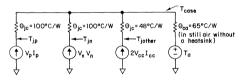

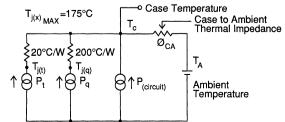

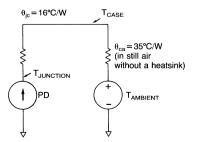

# Thermal Resistances<sup>1</sup>

| Package<br>CLC Pkg<br>Code                                  | Plastic DIP<br>P                  | Plastic SOIC<br>E                      | Ceramic side-<br>brazed DIP<br>D                               | CERDIP<br>B                                         |

|-------------------------------------------------------------|-----------------------------------|----------------------------------------|----------------------------------------------------------------|-----------------------------------------------------|

| CLC Part<br>Number                                          | $\theta_{JA}$                     | $\theta_{JA}$                          | $\theta_{JA}, \theta_{JC}$                                     | $\theta_{_{JA}}, \theta_{_{JC}}$                    |

| CLC110<br>CLC114<br>CLC115<br>CLC400<br>CLC401              | 100<br>75<br>75<br>100<br>100     | 125<br>75<br>75<br>125<br>125          | 100, 28<br>75, 28<br>75, 28<br>100, 28<br>100, 28              | 120, 50<br>TBD<br>120, 50<br>120, 50                |

| CLC402<br>CLC404<br>CLC406<br>CLC409<br>CLC410              | 100<br>100<br>100<br>100<br>100   | 125<br>125<br>125<br>125<br>125<br>125 | 100, 28<br>100, 28<br>100, 28<br>100, 28<br>100, 28<br>100, 28 | 100, 50<br>100, 50<br>120, 50<br>100, 50<br>100, 50 |

| CLC411<br>CLC412<br>CLC414<br>CLC415<br>CLC420              | 100<br>100<br>75<br>75<br>100     | 125<br>125<br>75<br>75<br>125          | 75, 28<br>75, 28<br>100, 28                                    | TBD<br>100, 50<br>TBD<br>TBD<br>100, 50             |

| CLC422<br>CLC425<br>CLC430<br>CLC501<br>CLC502              | 100<br>100<br>100<br>100<br>100   | 125<br>125<br>125<br>125<br>125<br>125 | 100, 28<br>100, 28<br>100, 28<br>100, 28                       | 100, 50<br>120, 50<br>100, 50<br>100, 50<br>100, 50 |

| CLC505 <sup>2</sup><br>CLC520<br>CLC522<br>CLC532<br>CLC533 | 100<br>75<br>75<br>75<br>75<br>75 | 125<br>75<br>75<br>75<br>75<br>75      | 100, 28<br>75, 28<br>TBD<br>75, 28                             | 100, 50<br>TBD<br>TBD<br>TBD                        |

$^{1}\text{Typical, }^{\circ}\text{C/W},$  ambient temperature 25°C, still air  $^{2}\text{R}_{\text{p}}\text{=}33\text{k}\Omega$

Comlinear's products are Electro Static Discharge (ESD) sensitive and are designed, processed, handled and packaged with consideration to both optimal ESD protection and product high performance.

Ratings listed below are based on criteria set forth per MIL-STD-883, Method 3015. Device ESD classifications are:

- Class 1: 0 to 1999 volts Class 2:

- 2000 to 3999 volts Class 3:

- 4000 volts and above

| Part   |       | Part   |       |

|--------|-------|--------|-------|

| Number | Class | Number | Class |

| CLC103 | 1     | CLC411 | 1     |

| CLC104 | 1     | CLC412 | 1     |

| CLC110 | 1*    | CLC414 | 1*    |

| CLC114 | 1*    | CLC415 | 1*    |

| CLC115 | 3*    | CLC420 | 2*    |

| CLC200 | 1     | CLC422 | 1*    |

| CLC201 | 1     | CLC425 | 1     |

| CLC203 | 1     | CLC430 | 3*    |

| CLC205 | 1     | CLC501 | 1*    |

| CLC206 | 1     | CLC502 | 1*    |

| CLC207 | 1     | CLC505 | 1*    |

| CLC220 | 1     | CLC520 | 1*    |

| CLC221 | 1     | CLC522 | 1     |

| CLC231 | 1*    | CLC532 | 1*    |

| CLC232 | 1     | CLC533 | 1     |

| CLC300 | 1     | CLC560 | 1     |

| CLC400 | 1*    | CLC561 | 1     |

| CLC401 | 1*    | CLC922 | 1     |

| CLC402 | 2*    | CLC925 | 1     |

| CLC404 | 1*    | CLC935 | 1     |

| CLC406 | 1*    | CLC936 | 1     |

| CLC409 | 1     | CLC940 | 1     |

| CLC410 | 1*    | CLC942 | 1     |

\*These parts have been tested and classified; others are considered Class 1 by design similarity. All products are marked with one ESD triangle symbol.

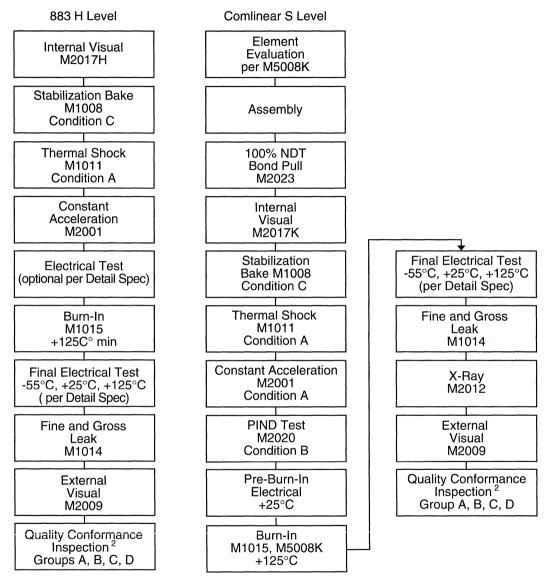

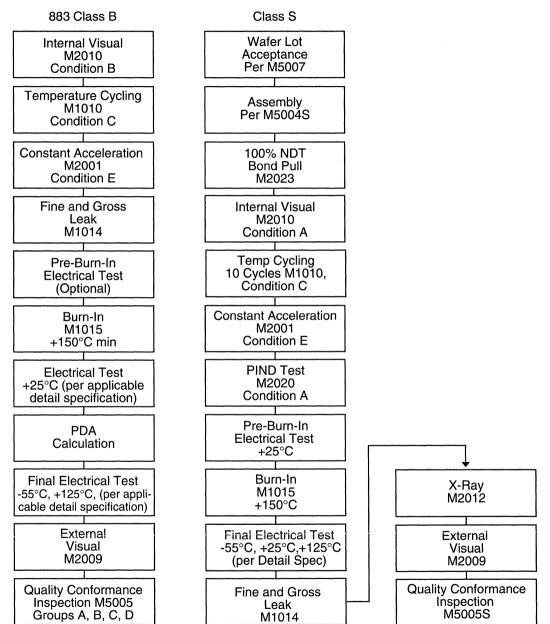

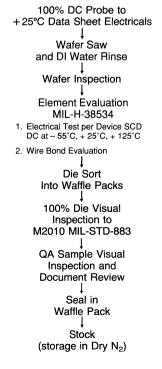

## **HYBRID**

la qu

<sup>1</sup>All processing flows are based on MIL-STD-883, MIL-H-38534 and are subject to change to correspond to current revisions. MXXXX references are to test methods in MIL-STD-883.

<sup>2</sup>Quality Conformance Inspection is per MIL-H-38534, option 1 (in-line).

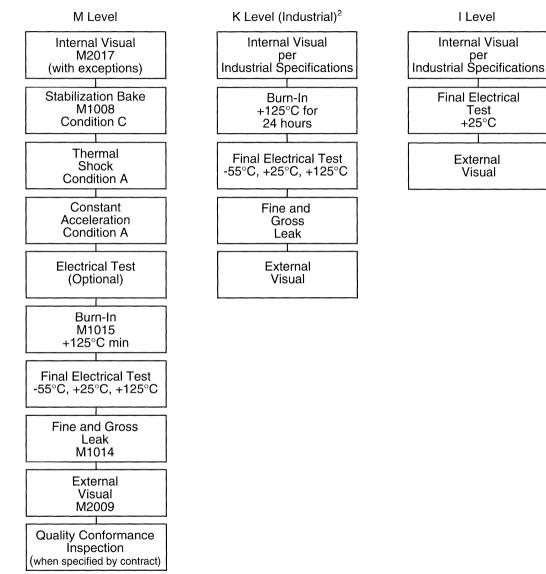

## HYBRID

<sup>1</sup>All processing flows are based on MIL-STD-883, MIL-H-38534 and are subject to change to correspond to current revisions. MXXXX references are to test methods in MIL-STD-883.

<sup>2</sup>Comlinear identification of an industrial grade flow. Not a 1772 "S Level" equivalent.

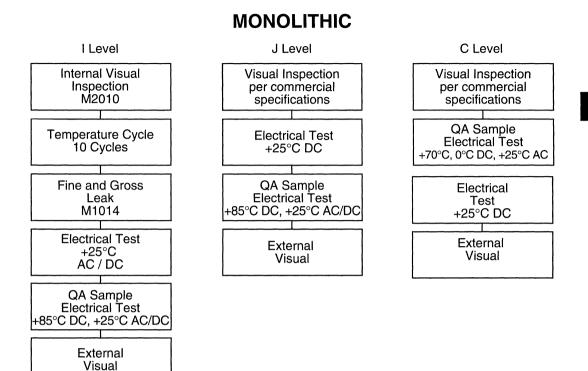

## MONOLITHIC

PROMESS

<sup>1</sup>All processing flows are based on MIL-STD-883 or MIL-M-38510 and are subject to change to correspond to current revisions. MXXXX references are to test methods in MIL-STD-883.

<sup>1</sup>All processing flows are based on MIL-STD-883 or MIL-M-38510 and are subject to change to correspond to current revisions. MXXXX references are to test methods in MIL-STD-883.

Π¢

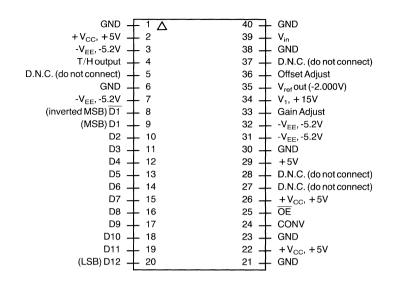

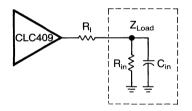

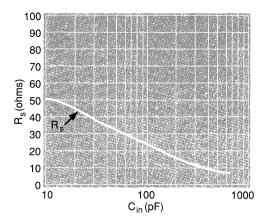

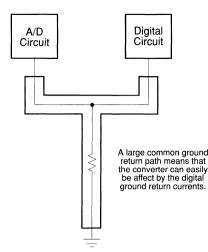

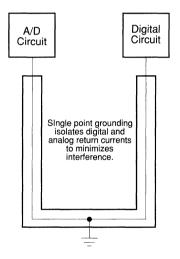

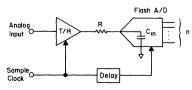

In-line Group A will be performed on inspection lots less than 500 pieces. Should end of line sampling techniques be utilized, the table below will be followed. Refer to detail specification for electrical tests within each subgroup.